# **C-RAM**<sup>™</sup> **2M** radiation-hardened non-volatile RAM

## Non-volatile memory product

The 256K × 8 radiationhardened non-volatile RAM with a single-bit error correction (SEC) is a highperformance, 266, 144-word × 8-bit randomaccess, non-volatile memory with industrystandard functionality. It is fabricated with BAE Systems' radiation-hardened, 0.25  $\mu$ m bulk CMOS technology, and is designed for use in systems operating in radiation environments. This NVRAM operates over an extended temperature range and requires a single 3.3V  $\pm$ 10 percent power supply.

## System definitions

A:0-18 Address input pins that select a particular 8-bit word within the memory array.

DQ:0-7 Bi-directional data pins that serve as data outputs during a read operation and as data inputs during a write operation.

CS Negative-active chip select when low level allows normal read or write operation. When high, CS forces the NVRAM to a precharge condition, holds the data output drivers in a high-impedance state, and disables write operations. If this signal is not used, it must be connected to GND.

WE Negative-active write-enable. When low (and WRT-DISABLE inactive), WE activates a write operation and holds the data output drivers in a high-impedance state. When high, WE allows normal-read operation.

OE Negative-active output-enable. When high, OE holds the data output drivers in a high-impedance state. When low, the data output driver state is defined by CS and WE. If this signal is not used, it must be connected to GND.

WRT-DISABLE Negative-active write-disable. When low (power-on reset, PROM mode, etc.), disables write operations while maintaining read-operation availability. When high, WRT-DISABLE permits write operations. If this signal is not used, it must be connected to VDD.

## A16-A17 -Block address decoder A13-A15 Sub-array decoder $((256 \times 32) x)$ A0-A7 Row address 8 x 4) x 8 decoder Memory cell array 8-bit word Internal RT-DISABLE input/output write WE timer Column address decoder OE DQ0-DQ7 A8-A12

## C-RAM family of products

## 2 Mb single chip

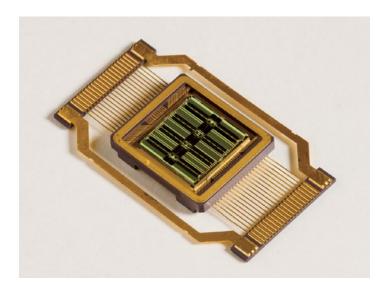

#### 256K x 8 C-RAM

40-lead flatpack (0.640 x 1.006 inches)

### Also available

4 Mb (512K x 8) monolithic and 20 Mb (512K x 40) MCM configurations

## Key features

# Minimum read cycle times

≤ 70 ns

# Minimum write-cycle times

<1000 ns

## Single power supply

$3.3 V \pm 10$  percent

# Operating temperature range

-40 to 110 degrees Celsius

## Low operating power

200 mW (typical) active read (70 ms)

130 mW (typical) active write (1000 ns)

60 mW (typical) standby (maximum)

## Write cycle endurance

> 105 cycles

#### **Data retention**

0.3 years at 90 degrees Celsius

1.1 years at 85 degrees Celsius

3.8 years at 80 degrees Celsius

13.5 years at 75 degrees Celsius

50 years at 70 degrees Celsius

## **Radiation levels**

Total ionizing dose:

$> 5 \times 10^5 \, \text{rad} \, (Si)$

Single event upset:

$1 \times 10^{-11}$  upsets/bit day

Neutron fluence:

$> 1 \times 10^{13}$  particles/cm<sup>2</sup>

Latchup-immune:

≤ 120 MeV-cm<sup>2</sup>/mg

#### For more information contact:

BAE Systems 9300 Wellington Road Manassas , Virginia 20110-4122

**T:** 571 364 7777

E: space.contact@baesystems.com

W: www.baesystems.com

Cleared for open publication by the U.S. Air Force Research Laboratory (AFRL) (Det 8), 02/12

## Disclaimer and copyright

This document gives only a general description of the product(s) and service(s) and, except where expressly provided otherwise, shall not form any part of any contract. From time to time, changes may be made in the products or the conditions of supply.

BAE SYSTEMS is a registered trademark of BAE Systems plc. @2017 BAE Systems. All rights reserved. CS-17-A28-04