## +28V 220 Amp Non-Isolated Power Controller

#### Features:

- Open frame / PC Board design

- Light weight 200 grams

- Operation temperature of -40°C to +85°C

- SPST, normally open DC power control

- I<sup>2</sup>T overload protected output with Switch Status Output

- I<sup>2</sup>c telemetry reporting of Switch voltage, current and base-plate temperature

- Power MOSFET output with Low on-state resistance

#### **DESCRIPTION:**

This non-Isolated DC Power Controller is a low mass open construction DC switch intended for applications within an enclosure. In addition to load switching, the incorporated  $\rm I^2T$  overload protection / fault protection provides a circuit breaker function. A status output signals output switch conditions of On / Off and Overload. An  $\rm I^2c$  interface communicates switch voltage, current and base plate temperature.

MOSFETs output switch provides soft start and low On voltage drop for cool operation.

The Logic Control input operates from a bias supply of 18 to 32V.

The Power Controller combines the functionality of a relay and circuit breaker. Output current is monitored for over-current with an I²T trip curve. Fault currents beyond the I²T trip limits are terminated instantly. Over-current conditions include Over-Load and Shorted Output during Turn-On. An open-collector Output Status is available to indicate the State of the Output Switch MOSFETs. The output remains blocked until the short is removed and the unit reset. Output Status is an Active Low for Control Off or Tripped condition and High into a pull up resistance for a (Control High) Normally On Output State. Controlling the IPC Off then back on resets a Tripped condition.

## Application:

28 Volts DC, 220 Amp Power Switching

### **ABSOLUTE MAXIMUM RATINGS**

| Load Voltage <sup>1</sup> | 100 VDC                                                         |

|---------------------------|-----------------------------------------------------------------|

| Load Current <sup>2</sup> | Not more Than 5 Times Rated Operating Current / Self Protecting |

|                           | -0.6 to 32 VDČ                                                  |

|                           | 1 Volt above V <sub>DD</sub> / 1 Volt below Return              |

|                           | -40°C to +85°C Case                                             |

|                           | 55°C to +125°C                                                  |

# Notes:

<sup>1</sup> Reversing output polarity may cause permanent damage

<sup>1</sup> The (circuit breaker) I<sup>2</sup>t function immediately terminates surge currents per Figure 2 or 3.

**ELECTRICAL CHARACTERISTICS:** T<sub>C</sub> = -40°C to 85°C unless specified.

| PARAMETER                                            | TEST CONDITIONS                    | MIN  | TYP     | MAX     | UNITS    |

|------------------------------------------------------|------------------------------------|------|---------|---------|----------|

| Output characteristics                               |                                    |      |         |         |          |

| Operating Voltage                                    | Intended system voltage            |      | 28      |         | VDC      |

| Continuous blocking voltage                          | Output device Rating               |      |         | 95      | VDC      |

| Rated Output Current                                 | 28V                                |      |         | 220     | ADC      |

| Load Start current for up to 100ms adjust range      | 28V                                |      | 440     |         | ADC      |

| Maximum On Stage Voltage drop                        | 25°C @ 220A                        |      | 0.7     |         | VDC      |

| On-state resistance, R <sub>ds</sub>                 | 25°C @ 220A                        |      | 3       |         | mOhms    |

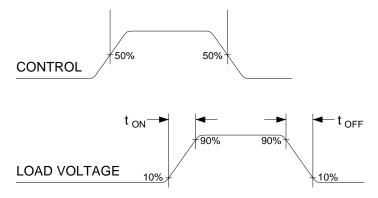

| Turn-on time / Rise Time                             | Figure 2                           |      | 4.0/1.0 | 5.0/3.0 | mS       |

| Turn-off time / Fall Time                            | Figure 2                           |      | 4.0/1.0 | 5.0/3.0 | mS       |

| Maximum Off State leakage                            | @ Continuous Blocking Voltage      |      |         | 5       | mA       |

| Snubbing                                             | Externally required                |      |         |         |          |

| Input characteristics CMOS configurations (Figure 1) |                                    |      |         |         |          |

| Bias supply range, V <sub>DD</sub>                   |                                    | 18   | 28      | 32      | VDC      |

| Bias current                                         |                                    | 1    | 80      | 90      | mA       |

| Control voltage range                                |                                    | -0.5 |         | 5.5     | VDC      |

| Turn-on voltage                                      |                                    | 0.0  | 2.9     | 0.0     | VDC      |

| Turn-off voltage                                     |                                    |      | 2.9     |         | VDC      |

| Status Output Specification                          |                                    |      | 2.5     |         | VB0      |

| Trip Reset Time                                      | Remove overload & Cycle input      | 50   |         |         | mS       |

| Status Supply Voltage (open Collector)               | Remove overload & Cycle Input      | 30   |         | 32      | VDC      |

| Status off leakage current                           | VS = 35 VDC                        |      |         | 4       | μADC     |

|                                                      |                                    |      |         |         | VDC      |

| Status on voltage                                    | I <sub>STATUS</sub> = 5 MA @ 25°C  |      |         | 0.4     |          |

| High-To-Low Transition Time                          | I <sub>STATUS</sub> = 5 MA         |      | 20      | 50      | μS       |

| General Specifications                               | @ 25°C                             |      |         |         |          |

| Dielectric withstanding                              | Power to I <sup>2</sup> c circuits | 500  |         |         | VDC      |

| Junction temperature                                 |                                    |      |         | 150     | °C       |

| Thermal resistance, $\theta_{JC}$                    |                                    |      |         | 0.3     | °C/W     |

| Output Capacitance                                   |                                    |      | 30,000  |         | pF       |

| Input to Output Capacitance                          |                                    |      | 250     |         | pF       |

| Data Communication I <sup>2</sup> c B / Phase 2 - 3  |                                    |      |         |         |          |

| Address                                              | 4 bits / jumper programmable       |      |         |         |          |

| Data:                                                |                                    |      |         |         |          |

| Switch Voltage / Resolution                          | 40.96V full scale / 12 Bit A to D  |      | 10      |         | mV / BIT |

| Switch Voltage / Accuracy                            |                                    |      | ±5%     |         |          |

| Output Current / Resolution                          | 409.6A full scale / 12 Bit A to D  |      | 100     |         | mA / BIT |

| Output Current / Accuracy                            |                                    |      | ±5%     |         |          |

| Temperature / Resolution                             | 0°C and above 204.8°C Full scale   |      | 0.05°C  |         | °C / BIT |

| Temperature / Accuracy                               |                                    |      | 2.0°C   |         |          |

| Mass                                                 |                                    | 1    |         | 200     | gram     |

#### NOTES:

- 1) Minimum Commanded "Off "or "On" time is 100msec.

- These IPCs have load current memory. Allow 100 seconds between overload or shorted load restarts for full current startup.

- 3) Input transitions should be "bounce-less contact" with transitions of <1 msec.

- 4) Inductive loads must be suppressed for operational command transients and Internal Fault shutdown times as short as 5µs.

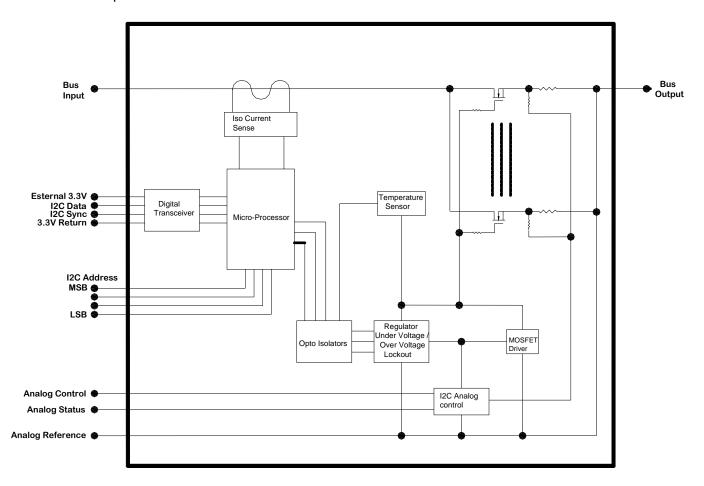

FIGURE 1

Preface: The proposed Bus Switch is based on the IPC family in general and the 53290 specifically. Modifications will conform to the specific Blackdog application.

Features include analog control commands and status monitoring. This ensures a "Hard" control of the Smart Switch minimizing accidental load power application. A  $\mu$ Processor based system communicating in I<sup>2</sup>C accesses Smart Power Switch makes available operating conditions such as device temperature, switched current, switch status and analog signals. The analog circuits and the  $\mu$ Processor are powered from the bus Input and require the bus to be active for any control or monitoring function.

A deliberate design feature of the system is to power up in the "off" condition. After the application of Bus Power to the input, the analog control must be brought to a "0" off state then to "1" on state to activate the system. A resistive pull-down is also part of the control circuit to ensure an Off condition in the event of an open control line. Switch turn on time is controlled with a compromise of limiting power dissipation and the ability to power up capacitive loads. An I²t feature from is the 53290 is incorporated with a 2X let-through current for up to 100msec at which the switch will latch Off until the analog control is cycled low then back on.

There is no-board clamping or snubbing for this application. The rational is there are circuits and functions both from the bus input and output that already require transient protection. These external protections will be relied on unless otherwise specified.

Figure 2 Switching Characteristics

| Turn on into Short Sequence |         |         |     |     |          | Short while on Sequence |     |     |     |          |

|-----------------------------|---------|---------|-----|-----|----------|-------------------------|-----|-----|-----|----------|

| Control                     | 0       | 1       | 1   | 0   | 1        | 1                       | 1   | 1   | 0   | 1        |

| I out                       | Off     | Off     | Off | Off | On       | On                      | Off | Off | Off | On       |

| Switch<br>Status            | 0       | 0       | 0   | 0   | Open "1" | Open "1"                | 0   | 0   | 0   | Open "1" |

| Shorted<br>Output           | Shorted | Shorted | Х   | Off | Off      | Off                     | On  | Х   | Χ   | Off      |

Truth Table - Short circuit and Status

#### Notes:

- 1. Unit Powers up in the OFF condition with application of Primary power.

- 2. Fault Status reports only when Primary Power is present.

- 3. An OFF Control to ON Control transition is required to first turn the Unit On.

- 4. A loss of V<sub>DD</sub> will return the output state to OFF.

- 5. Truth Table Power sequencing: Output Status open collector pull-up resistor is assigned a separate and always On voltage producing a "1" when "Open".

### I<sup>2</sup>c Data Protocol:

The data string is organized as an 8 byte string.

| String (8 bytes) | Data               |

|------------------|--------------------|

| 0                | LSB Status Input   |

| 1                | MSB Status Input   |

| 2                | LSB Switch Voltage |

| 3                | MSB Switch Voltage |

| 4                | LSB Current Output |

| 5                | MSB Current Output |

| 6                | LSB Temperature    |

| 7                | MSB Temperature    |

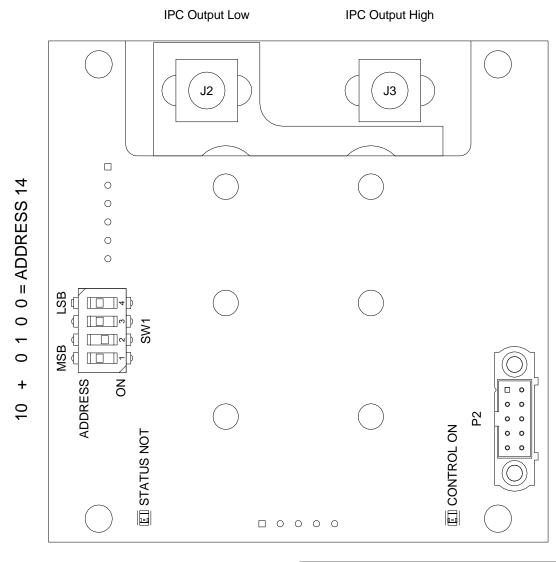

$I^2$ c address is 7 bits. The 4 bit address is located from bit 3, to bit 7. A count of 10 is added to the incoming address to position the 4 hardwired bits. Over bits 3 to 7.

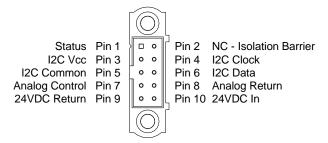

NOTE: Analog Return and 24VDC Return are not connected at the Power Controller to prevent ground loops at system level. These points must be connected external to the Power Controler for correct operation

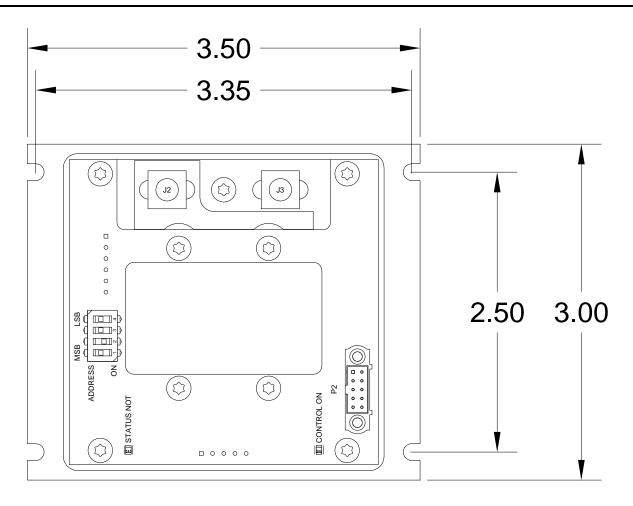

P2 Part Number: M80-5001042 P2 Mating Connector: M80-4551098

Output Connections:

Connector J2 Most Negative

Connector J3 Most Positive

Hardware Connections:

J2 and J3 uses 1/4-28 threaded bolts

MAX Torque for hardware is 10 in-lbs

Figure 3 Pin Assignment

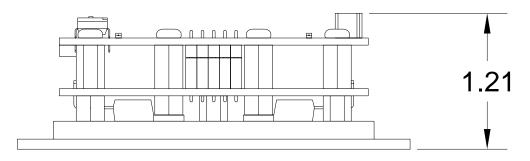

**Figure 4 Package Dimensions**

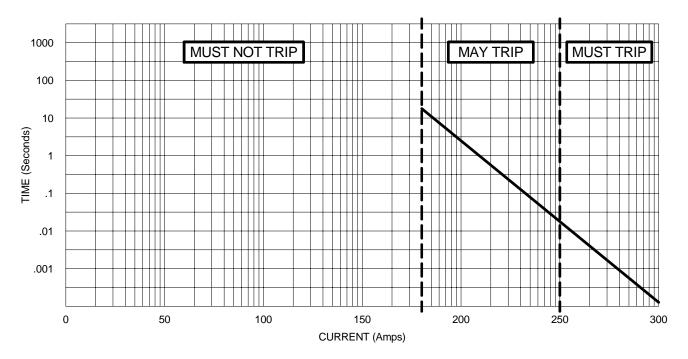

Figure 5 Trip Curve

## **TRIP CURVE NOTES:**

- 1. Output currents are interrupted in the Must Trip / May Trip / Must Not Trip per the following graph.

- 2. Output (sustaining) Current is 10 to 90A.

- 3. Load fault current from the "ON" operating condition are limited by the source and load impedance.

- 4. Over current and fault trip currents terminate abruptly and are snubbed for up to 3µH of load inductance.

## **Product Status:**

This document contains information on a product under development. Micropac reserves the right to change this product.