# TriScape100

# **Interface Control Document**

Document Number: 033807

Author(s): E. Grobbelaar, J. Vos

Revision: 3

<u>Controlled document note:</u> It is the user's responsibility to verify that the version of any printed documentation matches the configuration controlled version.

# **Document History**

| Revision | Date       | Details                                                                                  |

|----------|------------|------------------------------------------------------------------------------------------|

| 1        | 2019-06-27 | First release of document.                                                               |

| 2        | 2019-06-27 | First formal release of document.                                                        |

| 3        | 2020-07-24 | Updated Sections 3, 4 and 5, including various updates for revision 2 of the electronics |

# **Table of Contents**

| 1. Introdu | ction                                                                      | 9  |

|------------|----------------------------------------------------------------------------|----|

| 1.1        | Identification                                                             | 9  |

| 1.2        | Intended Use                                                               | 9  |

| 1.3        | Context and Summary                                                        | 9  |

| 2. Referer | nced Documents                                                             | 10 |

| 3. System  | Description and Context                                                    | 11 |

| 3.1        | Physical Description                                                       | 11 |

| 3.2        | Physical Properties                                                        | 14 |

| 4. Descrip | tion of System Interfaces                                                  | 17 |

| 4.1        | Interface Identification and Definition                                    | 17 |

| 4.2        | Optical Interface                                                          | 18 |

|            | 4.2.1 Interface 1: Target in View to TriScape100                           | 18 |

| 4.3        | Mechanical Interfaces                                                      | 19 |

|            | 4.3.1 Interface 2: xScape100 VIS OFE to Satellite Components               | 19 |

|            | 4.3.2 Interface 5: TriScape100 Control Electronics to Satellite Components | 20 |

| 4.4        | Thermal Interfaces                                                         | 23 |

|            | 4.4.1 Interface 3: xScape100 VIS OFE to Satellite Components               | 23 |

|            | 4.4.2 Interface 4: TriScape100 Sensor Unit to Satellite Components         | 23 |

|            | 4.4.3 Interface 6: TriScape100 Control Electronics to Satellite Components | 23 |

| 4.5        | Electrical Interfaces                                                      | 24 |

|            | 4.5.1 Interface 7: Satellite Components to TriScape100 Control Electronics | 24 |

| 4.6        | Environmental Interfaces                                                   | 39 |

|            | 4.6.1 Thermal Radiation Interface                                          | 39 |

|            | 4.6.2 Cosmic Radiation Interfaces                                          | 39 |

| 5. Environ | mental Requirements                                                        | 40 |

| 5.1        | Transportation                                                             | 40 |

|            | 5.1.1 Temperature                                                          | 40 |

|            | 5.1.2 Humidity                                                             | 40 |

|            | 5.1.3 Shock/Vibration                                                      | 40 |

|            | 5.1.4 Cleanliness                                                          | 40 |

| 5.2        | Storage                                                                    | 40 |

033807

iv

|     | 5.2.1   | Temperature                        | 40  |

|-----|---------|------------------------------------|-----|

|     | 5.2.2   | Humidity                           | 40  |

|     | 5.2.3   | Cleanliness                        | 40  |

| 5.3 | Asseml  | oly, Integration and Testing       | .41 |

|     | 5.3.1   | Shock                              | 41  |

|     | 5.3.2   | Mechanical Interface with OFE      | 41  |

| 5.4 | In-Orbi | t                                  | .41 |

|     | 5.4.1   | Survivable Temperature             | 41  |

|     | 5.4.2   | Operating Temperature              | 41  |

|     | 5.4.3   | Operating Temperature Gradients    | 41  |

|     | 5.4.4   | Outgassing of Satellite Components | 41  |

|     |         |                                    |     |

# List of Figures

| Figure 3-1: Typical CubeSat System Diagram                                   | 11 |

|------------------------------------------------------------------------------|----|

| Figure 3-2: TriScape100 with Axis Definition                                 | 12 |

| Figure 3-3: Exploded View of TriScape100 Sensor Unit and Control Electronics | 13 |

| Figure 3-4: Imager Ground Projection                                         | 14 |

| Figure 3-5: Centre of Mass Position                                          | 16 |

| Figure 4-1: Interface Identification Diagram                                 | 17 |

| Figure 4-2: OFE Mounting Interface Dimensions                                | 19 |

| Figure 4-3: CE Mechanical Drawing                                            | 21 |

| Figure 4-4: CE and High-Speed Connector Mounting Hole Details                | 21 |

| Figure 4-5: CE with Bi-Lobe Breakout Adapter                                 | 22 |

| Figure 4-6: CE with Datamate Breakout Adapter                                | 22 |

| Figure 4-7: CE Mounting Position Relative to OFE                             | 23 |

| Figure 4-8: High-Speed Data Connector (P5)                                   | 28 |

| Figure 4-9: I <sup>2</sup> C Command Transaction                             | 31 |

| Figure 4-10: I <sup>2</sup> C Request Transaction                            | 32 |

| Figure 4-11: SPI Command Transaction                                         | 32 |

| Figure 4-12: SPI Request Transaction                                         | 33 |

| Figure 4-13: Standard High-Speed Link Byte Transfer Cycle Waveform           | 34 |

| Figure 4-14: Single vs Two Data Lane Byte Ordering                           | 34 |

| Figure 4-15: High-Speed Link HS_RR Operation                                 | 35 |

| Figure 4-16: USART Data Transfer                                             | 35 |

| Figure 4-17: USART US_nCTS Operation                                         | 36 |

| Figure 4-18: USART US_EOF Operation                                          | 36 |

033807

| Figure 4-19: Imager Data Packet Description             | 37 |

|---------------------------------------------------------|----|

| Figure 4-20: Data Output Example for an Imaging Session | 38 |

# **List of Tables**

| Table 2-1: Referenced Documents                                        | 10 |

|------------------------------------------------------------------------|----|

| Table 3-1: System and Component Functional Description                 | 11 |

| Table 3-2: Physical Properties                                         | 14 |

| Table 3-3: Natural Frequencies of the Imager from 0 - 2000 Hz          | 15 |

| Table 4-1: Interface Definition                                        | 18 |

| Table 4-2: OFE Mounting Interface Specifications                       | 20 |

| Table 4-3 : CubeSat Kit Bus Compatible PC-104 Header (H1) Pinout       | 24 |

| Table 4-4 : CubeSat Kit Bus Compatible PC-104 Header (H2) Pinout       | 25 |

| Table 4-5 : High-Speed Interface Connector (P5) Pinout                 | 26 |

| Table 4-6 : High-Speed Interface Bi-Lobe Connector (P9) Pinout         | 28 |

| Table 4-7 : High-Speed Interface Datamate Connector (P9) Pinout        | 29 |

| Table 4-8: Nominal Imager Power Consumption Values at Room Temperature | 30 |

# List of Abbreviations

| Abbreviation | Description                                         |  |

|--------------|-----------------------------------------------------|--|

| AIT          | Assembly, Integration and Testing                   |  |

| CE           | Control Electronics                                 |  |

| CVCM         | Collected Volatile Condensable Material             |  |

| DC           | Direct Current                                      |  |

| FPGA         | Field Programmable Gate Array                       |  |

| 10           | Input/Output                                        |  |

| ISO          | International Organization for Standardization      |  |

| LVCMOS       | Low Voltage Complementary Metal Oxide Semiconductor |  |

| LVDS         | Low Voltage Differential Signalling                 |  |

| MSB          | Most Significant Bit                                |  |

| NC           | No Connect                                          |  |

| OFE          | Optical Front-End                                   |  |

| PCB          | Printed Circuit Board                               |  |

| SPI          | Serial Peripheral Interface                         |  |

| STP          | Shielded Twisted Pair                               |  |

| TML          | Total Mass Loss                                     |  |

### 1. Introduction

#### 1.1 Identification

Item Description: TriScape100

Simera Item Number: 034293

#### 1.2 Intended Use

This document describes the interfaces and environmental conditions of the TriScape100 Imager.

#### 1.3 Context and Summary

The TriScape100 is an electro-optical snapshot imaging system employing a CMOSIS CMV12000 sensor with integrated RGB Bayer filter in the visible spectral range. The TriScape100 is produced by Simera Sense and is intended for earth observation applications. It is primarily designed to be implemented as part of an optical payload in a CubeSat. Its compact form factor allows for direct implementation into a 3U CubeSat structure; however, the TriScape100 can also be used as part of larger satellite systems.

This Interface Control Document identifies, defines and describes the interfaces between the TriScape100 and the surrounding satellite components, as well as between the TriScape100 and its environment.

# 2. Referenced Documents

Table 2-1 lists documents that are referenced in this document. In the event of conflict between the contents of the reference documents and this document, this document shall take precedence.

**Table 2-1: Referenced Documents**

| Ref. #                                                                                                                                       | Reference                                                                                                                                                           |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [1]                                                                                                                                          | Outgassing Data for Selecting Spacecraft Materials. [Online]. Available: <a href="https://outgassing.nasa.gov/">https://outgassing.nasa.gov/</a> [2018, October 24] |  |  |

| [2] NXP I2C-bus specification and User Manual. [Online]. Available:<br>https://www.nxp.com/docs/en/user-guide/UM10204.pdf [2018, October 24] |                                                                                                                                                                     |  |  |

For undated references, the latest released version of the reference document applies. For dated references, subsequent versions of the document do not apply. It is best practice to always refer to the latest released version. Unless otherwise stated, web links referenced above were last accessed at the release date of the current version of this document.

# 3. System Description and Context

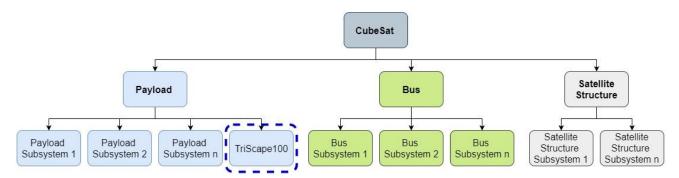

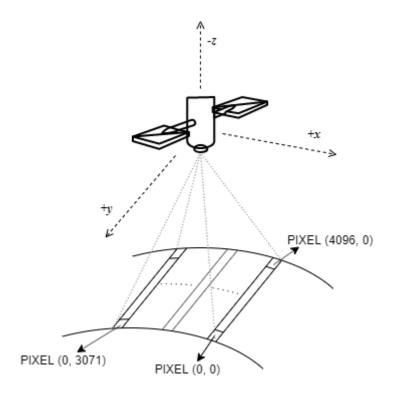

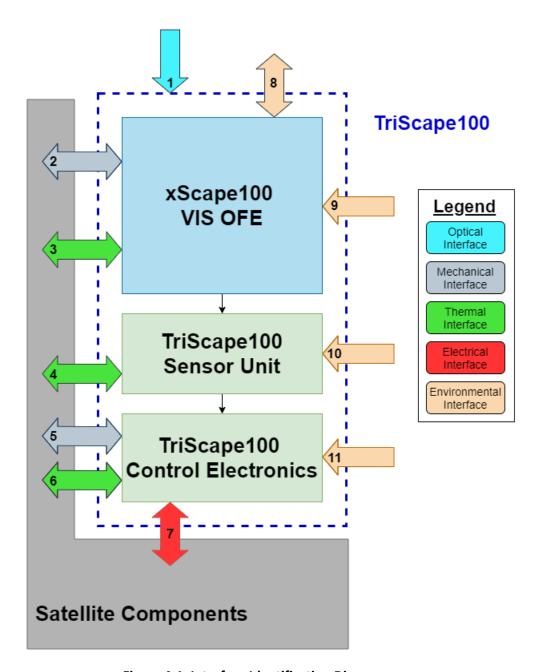

The TriScape100 captures electromagnetic radiation in the visible spectrum, focuses the radiation on a sensor and converts the focused electromagnetic radiation into electrical signals. The TriScape100 typically forms part of the payload of a satellite and is shown in the context of a typical CubeSat diagram in Figure 3-1 below.

Figure 3-1: Typical CubeSat System Diagram

# 3.1 Physical Description

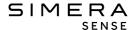

The TriScape100, hereafter referred to as the "Imager", consists of several subassemblies which comprises of the xScape100 VIS Optical Front-End (OFE), the TriScape100 Sensor Unit and the TriScape100 Control Electronics. Table 3-1 provides a functional description of the Imager and its components.

Imager/Component ID **Primary Functions** TriScape100 Collects electromagnetic radiation and 1 converts it into electrical signals 1.1 xScape100 VIS OFE Focuses the collected electromagnetic radiation onto an imaging sensor 1.2 TriScape100 Sensor Unit Positions the sensor on the focal plane and converts the focused electromagnetic radiation into electrical signals 1.3 TriScape100 Control Powers and drives the sensor unit, as well **Electronics** as provides storage space for the captured images

**Table 3-1: System and Component Functional Description**

Figure 3-2 illustrates the physical system subassemblies and provides the axis definition. In Figure 3-2 the TriScape100 Control Electronics is shown with the CubeSat Kit Bus compatible PC-104 header and with the Bi-Lobe Breakout Adapter option included (see section 4.5.1.1 for these physical electrical interface options).

Figure 3-2: TriScape100 with Axis Definition

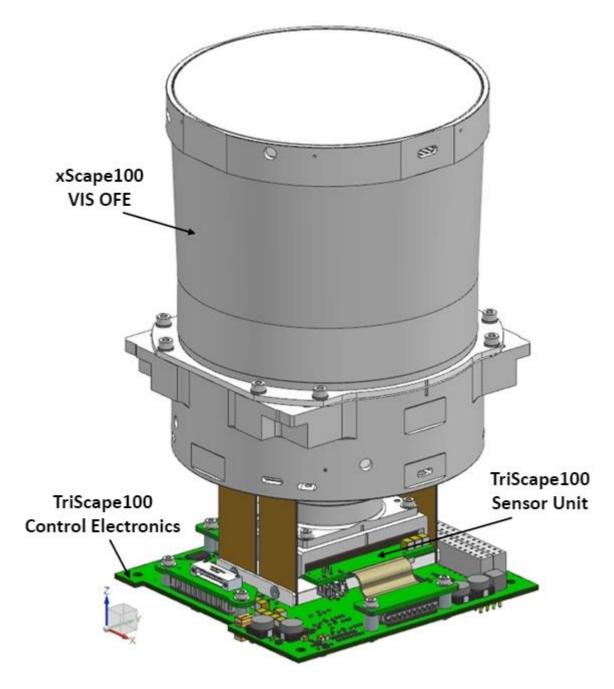

An exploded view of the TriScape100 Sensor Unit and the TriScape100 Control Electronics is shown in Figure 3-3. The TriScape100 Control Electronics is shown without the CubeSat Kit Bus compatible PC-104 header and with the Bi-Lobe Breakout Adapter option (see section 4.5.1.1 for these physical electrical interface options).

Figure 3-3: Exploded View of TriScape100 Sensor Unit and Control Electronics

Figure 3-4 shows the Imager ground projection and the position of the first pixel clocked out from each line of each band with respect to the Imager axis definition.

Figure 3-4: Imager Ground Projection

# 3.2 Physical Properties

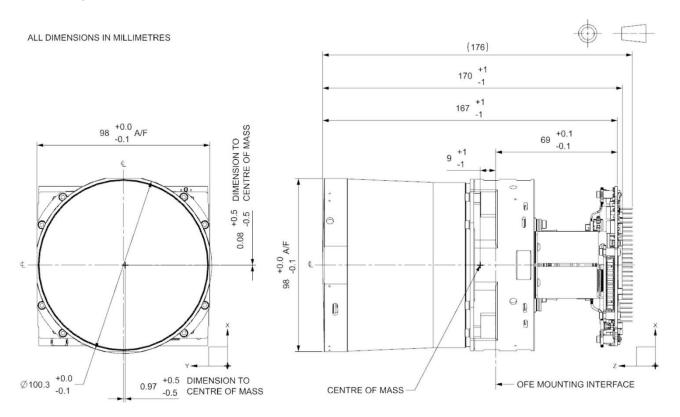

The physical properties of the Imager are presented in Table 3-2. The reference axis system used to define the moments of inertia and centre of mass position is located at the geometric centre of the OFE's mounting points which is shown in Figure 4-2.

**Property** Unit **Value** Mass kg 1.1 (± 5%) Moments of Inertia 3.6 x 10<sup>-3</sup> (± 5%) kg.m<sup>2</sup> 3.5 x 10<sup>-3</sup> (± 5%) kg.m<sup>2</sup>  $I_{vv}$ 1.5 x 10<sup>-3</sup> (± 5%) kg.m<sup>2</sup>  $I_{zz}$ Centre of Mass -0.08 (± 0.5) See Figure 3-5  $\mathsf{mm}$ -0.97 (± 0.5) See Figure 3-5 mm У 9 (± 1.0) See Figure 3-5 mm Z

**Table 3-2: Physical Properties**

Table 3-3 provides the natural frequencies of the Imager when it is mounted on an infinitely stiff interface at its four mounting points which is shown in Figure 4-2.

Table 3-3: Natural Frequencies of the Imager from 0 - 2000 Hz

| Mode Number | Frequency [Hz] |

|-------------|----------------|

| 1           | 684            |

| 2           | 705            |

| 3           | 800            |

| 4           | 854            |

| 5           | 891            |

| 6           | 996            |

| 7           | 1020           |

| 8           | 1072           |

| 9           | 1157           |

| 10          | 1587           |

| 11          | 1691           |

| 12          | 1718           |

| 13          | 1820           |

| 14          | 1839           |

| 15          | 1855           |

| 16          | 1933           |

| 17          | 1947           |

| 18          | 1997           |

Figure 3-5 presents the envelope dimensions of the Imager and indicates the position of the centre of mass relative to the OFE's mounting points. The maximum dimension of 176 mm is only applicable if the CubeSat Kit Bus compatible PC-104 header has been selected (see section 4.5.1.1.1).

Figure 3-5: Centre of Mass Position

# 4. Description of System Interfaces

#### 4.1 Interface Identification and Definition

The various interfaces between the Imager and the satellite components, as well as between the Imager and its environment, are shown graphically in Figure 4-1 below. The satellite components are herein defined as being all components which do not form part of the Imager and as such includes the satellite structure.

Note: For analysis purposes it is assumed that there is no thermal interface via the wiring harnesses.

Figure 4-1: Interface Identification Diagram

The interfaces identified in Figure 4-1, are defined in Table 4-1 below. The descriptions of the interfaces are presented in the subsections that follow.

**Table 4-1: Interface Definition**

| Interface Number | Interface Type                       | Interface From                  | Interface To                       |

|------------------|--------------------------------------|---------------------------------|------------------------------------|

| 1                | Optical                              | Target in View                  | TriScape100                        |

| 2                | Mechanical                           | xScape100 VIS OFE               | Satellite Components               |

| 3                | Thermal                              | xScape100 VIS OFE               | Satellite Components               |

| 4                | Thermal                              | TriScape100 Sensor<br>Unit      | Satellite Components               |

| 5                | Mechanical                           | TriScape100 Control Electronics | Satellite Components               |

| 6                | Thermal                              | TriScape100 Control Electronics | Satellite Components               |

| 7                | Electrical<br>(Power and Control)    | Satellite Components            | TriScape100 Control<br>Electronics |

| 8                | Environmental<br>(Thermal Radiation) | xScape100 VIS OFE               | Environment                        |

| 9                | Environmental (Cosmic Radiation)     | Environment                     | xScape100 VIS OFE                  |

| 10               | Environmental (Cosmic Radiation)     | Environment                     | TriScape100 Sensor Unit            |

| 11               | Environmental<br>(Cosmic Radiation)  | Environment                     | TriScape100 Control<br>Electronics |

# 4.2 Optical Interface

# 4.2.1 Interface 1: Target in View to TriScape100

The TriScape100 has an optical interface at its front aperture with a diameter 95 mm. It has an across-track full field of view of 2.2 degrees, and along-track full field of view of 1.7 degrees. The function of this interface is to enable the collection of electromagnetic radiation by the OFE. This optical interface shall remain unobscured during imaging to ensure optimal performance of the Imager.

The platform shall track and point the Imager to the target. Platform jitter shall be minimized for optimal image quality.

#### 4.3 Mechanical Interfaces

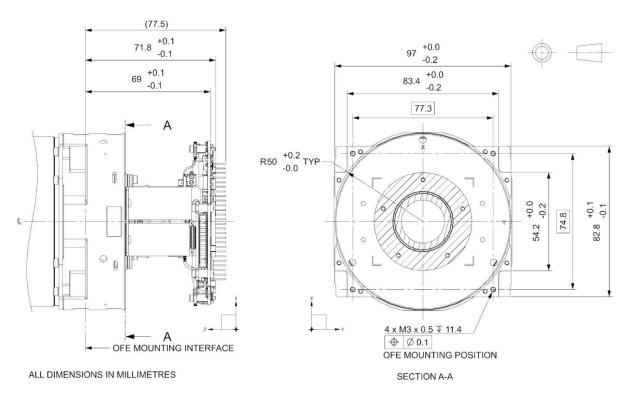

#### 4.3.1 Interface 2: xScape100 VIS OFE to Satellite Components

The OFE interfaces mechanically with the satellite structure via four threaded mounting points. The function of this interface is to secure the OFE to the applicable satellite components and act as the main structural support for the Imager.

The mating interface which is bolted to the OFE shall have four through holes with a diameter of 3.4 mm or larger. These through holes shall be spaced to match the hole spacing of the four M3 threaded holes (as shown in Figure 4-2) exactly and shall have a positional tolerance of 0.1 mm. All interfaces which mate directly to the mounting interface of the OFE shall be coplanar and have a flatness tolerance of 50  $\mu$ m or smaller. In addition, the mating interfaces shall have a N7 or smoother surface finish (this is equivalent to a surface finish with an average roughness of Ra = 1.6  $\mu$ m).

Caution shall be exercised during the assembly of any mechanics to the mounting interface of the OFE. Any mechanics which will be mounted to the OFE, shall first be secured to the OFE's mounting interface, only then shall the mechanics be joined to the rest of the satellite structure. This shall be done to ensure that the mounting surfaces of the OFE remain coplanar in the z-direction. Figure 4-2 provides the dimensions of the OFE's mounting interface. The 77.5 mm dimension is only applicable if the CubeSat Kit Bus compatible PC-104 header has been selected (see section 4.5.1.1.1).

Figure 4-2: OFE Mounting Interface Dimensions

The details of the mounting interface are specified in Table 4-2 below.

**Table 4-2: OFE Mounting Interface Specifications**

| Description                                         | Value                        |

|-----------------------------------------------------|------------------------------|

| Interface Material                                  | Titanium Grade 5 (Ti-6Al-4V) |

| Interface Surface Finish                            | Bare Ti-6Al-4V               |

| Interface Surface Fiffish                           | N7 surface finish            |

| Flatness                                            | < 20 μm                      |

| Number of Mounting Locations                        | 4                            |

| Thread Specification                                | M3 x 0.5 (see Figure 4-2)    |

| Depth of Thread Supplied in OFE                     | 11.4 mm                      |

| Fastener Torque (for stainless steel A4-70 fastener |                              |

| material). All fasteners shall be staked using      | 1 Nm                         |

| Scotch Weld EC2216 adhesive or equivalent.          |                              |

### 4.3.2 Interface 5: TriScape100 Control Electronics to Satellite Components

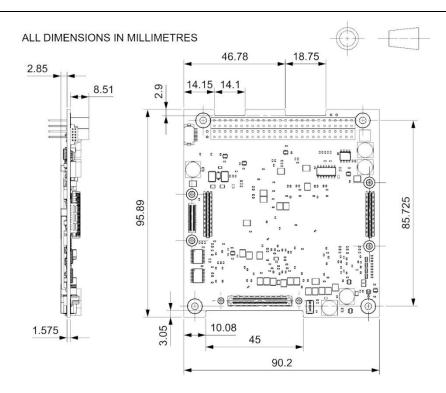

The TriScape100 Control Electronics (CE) interfaces mechanically with the satellite components through the four mounting holes located on the edges of the printed circuit board (PCB). These four mounting holes are through holes in the PCB and their spacing conforms to the PC-104 standard. The function of this interface is to secure the PCB to the applicable satellite component and act as main structural support for the CE. Figure 4-3 displays the dimensions of the CE PCB, as well as the height of the components on both sides of the PCB. The CE is shown with the CubeSat Kit Bus compatible PC-104 header (see section 4.5.1.1.1) included.

Figure 4-3: CE Mechanical Drawing

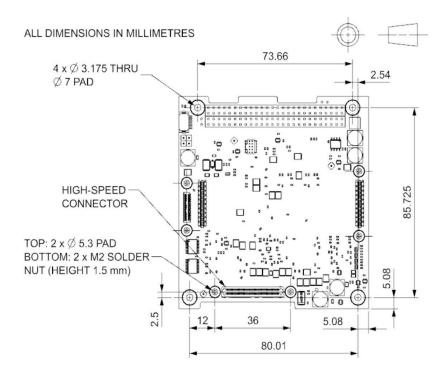

In Figure 4-4 below, the mounting details of the CE, as well as of the high-speed connector interface on the CE PCB are shown in more detail.

Figure 4-4: CE and High-Speed Connector Mounting Hole Details

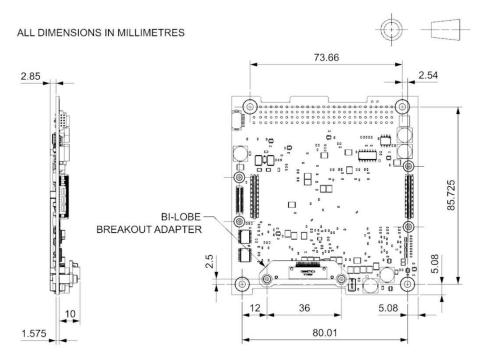

There are two breakout adapter options available for the high-speed interface on the CE (see section 4.5.1.1.2 for more details). Figure 4-5 shows the CE with the Bi-Lobe Breakout Adapter option.

Figure 4-5: CE with Bi-Lobe Breakout Adapter

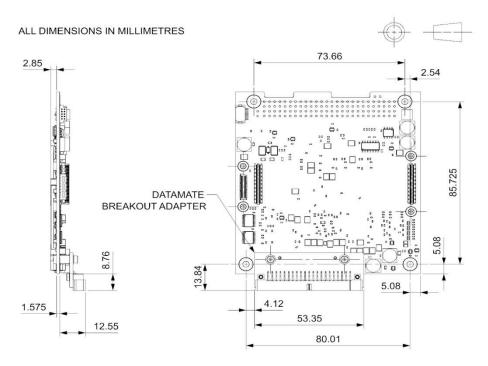

Figure 4-6 shows the CE with the Datamate Breakout Adapter option.

Figure 4-6: CE with Datamate Breakout Adapter

69 CONTROL ELECTRONICS MOUNTING INTERFACE 1.575 85.725 42.8 **(A)** 39.4 6009-28 80.01 0000 · 🗆 :1 O ⇔⊙ ·

Figure 4-7 shows the mounting position of the CE relative to the OFE.

Figure 4-7: CE Mounting Position Relative to OFE

4 x Ø 3.175 THRU - Ø 7 PAD

CONTROL ELECTRONICS MOUNTING LOCATIONS

#### 4.4 Thermal Interfaces

ALL DIMENSIONS IN MILLIMETRES

#### 4.4.1 Interface 3: xScape100 VIS OFE to Satellite Components

OFE MOUNTING POSITION

The mounting interface between the OFE and applicable satellite components facilitates heat transfer through thermal conduction between the OFE and the satellite components. In addition, thermal energy is also exchanged (by means of radiation) between the OFE and the surrounding satellite components. No specific requirement is placed on the amount of energy transmitted via conduction and radiation.

#### 4.4.2 Interface 4: TriScape100 Sensor Unit to Satellite Components

Thermal energy is exchanged by means of radiation between the TriScape100 Sensor Unit and the surrounding satellite components. No specific requirement is placed on the amount of energy transmitted via radiation.

### 4.4.3 Interface 6: TriScape100 Control Electronics to Satellite Components

The mounting points of the CE facilitate heat transfer through thermal conduction between the CE and the surrounding satellite components. In addition, thermal energy is also exchanged (by means of radiation) between the CE and the surrounding satellite components. No specific requirement is placed on the amount of energy transmitted via conduction and radiation.

#### 4.5 Electrical Interfaces

#### 4.5.1 Interface 7: Satellite Components to TriScape100 Control Electronics

This interface consists of a single or of multiple electrical connector(s) to act as interface between the CE and the applicable satellite component(s). The function of this interface is to transmit power, control and data to and from the CE.

#### 4.5.1.1 Physical Electrical Interfaces

# 4.5.1.1.1 PC-104 Interface (H1 and H2)

The CE supports a CubeSat Kit Bus compatible PC-104 header and its pin description is given in Table 4-3 and Table 4-4. The pins labelled 'Not Used' are not connected on the CE, while those labelled '5 V RETURN' are always connected for the power ground return. The rest of the pins (including 5 V and  $I^2$ C signals) are not connected by default but are configured through the product configuration sheet if and where they are connected. All pins labelled 'IOn'' are 3.3 V Low Voltage Complementary Metal Oxide Semiconductor (LVCMOS) compatible input/output pins. Those labelled ' $IVDSn\pm$ ' are routed differentially and can be used as LVDS pairs to implement SpaceWire, the standard high-speed data interface, or USART over LVDS. The PC-104 interface provides access to the power, control and data interfaces meaning it can be used as the only physical interface to the CE without requiring the high-speed interface.

Table 4-3: CubeSat Kit Bus Compatible PC-104 Header (H1) Pinout

| Pin | Signal                      | Pin | Signal                   |

|-----|-----------------------------|-----|--------------------------|

| 1   | 100                         | 2   | IO1                      |

| 3   | 102                         | 4   | IO3 / PowerCtrl / LVDS6- |

| 5   | IO4 / PowerCtrl / LVDS6+    | 6   | IO4 / PowerCtrl / LVDS6+ |

| 7   | IO5 / PowerCtrl / LVDS7+    | 8   | IO5 / PowerCtrl / LVDS7+ |

| 9   | IO6 / PowerCtrl / LVDS7-    | 10  | IO6 / PowerCtrl / LVDS7- |

| 11  | IO7 / PowerCtrl / LVDS3-    | 12  | Not Used                 |

| 13  | IO8 / PowerCtrl / LVDS3+    | 14  | IO8 / PowerCtrl / LVDS3+ |

| 15  | IO9 / PowerCtrl             | 16  | IO9 / PowerCtrl          |

| 17  | IO10                        | 18  | IO10                     |

| 19  | IO11                        | 20  | IO11                     |

| 21  | IO12 / I <sup>2</sup> C SCL | 22  | IO12                     |

| 23  | IO13 / I <sup>2</sup> C SDA | 24  | IO13                     |

| 25  | Not Used                    | 26  | Not Used                 |

| 27  | Not Used                    | 28  | Not Used                 |

| 29  | IO14 / LVDS5-               | 30  | IO15                     |

| 31  | IO16                        | 32  | IO17 / LVDS5+            |

| 33  | IO18                        | 34  | Not Used                 |

| 35  | IO19 / LVDS2-               | 36  | Not Used                 |

| 37  | Not Used                    | 38  | Not Used                 |

| Pin | Signal                      | Pin | Signal      |

|-----|-----------------------------|-----|-------------|

| 39  | IO20 / LVDS2+               | 40  | IO21        |

| 41  | IO22 / I <sup>2</sup> C SDA | 42  | Not Used    |

| 43  | IO23 / I <sup>2</sup> C SCL | 44  | Not Used    |

| 45  | 1-Wire Vcc                  | 46  | 1-Wire Data |

| 47  | 5 V Optional Input          | 48  | Not Used    |

| 49  | 5 V Optional Input          | 50  | Not Used    |

| 51  | 5 V Optional Input          | 52  | Not Used    |

Table 4-4: CubeSat Kit Bus Compatible PC-104 Header (H2) Pinout

| Pin | Signal                    | Pin | Signal                    |

|-----|---------------------------|-----|---------------------------|

| 1   | Not Used                  | 2   | Not Used                  |

| 3   | Not Used                  | 4   | Not Used                  |

| 5   | Not Used                  | 6   | Not Used                  |

| 7   | Not Used                  | 8   | Not Used                  |

| 9   | Not Used                  | 10  | Not Used                  |

| 11  | Not Used                  | 12  | Not Used                  |

| 13  | 5 V Optional Input        | 14  | Not Used                  |

| 15  | 5 V Optional Input        | 16  | 5 V Optional Input        |

| 17  | IO24 / PowerCtrl / LVDS4- | 18  | IO24 / PowerCtrl / LVDS4- |

| 19  | IO25 / PowerCtrl / LVDS4+ | 20  | IO25 / PowerCtrl / LVDS4+ |

| 21  | 1026                      | 22  | IO26                      |

| 23  | Not Used                  | 24  | Not Used                  |

| 25  | 5 V Optional Input        | 26  | 5 V Optional Input        |

| 27  | Not Used                  | 28  | Not Used                  |

| 29  | 5 V RETURN                | 30  | 5 V RETURN                |

| 31  | Not Used                  | 32  | 5 V RETURN                |

| 33  | Not Used                  | 34  | Not Used                  |

| 35  | Not Used                  | 36  | Not Used                  |

| 37  | Not Used                  | 38  | Not Used                  |

| 39  | Not Used                  | 40  | Not Used                  |

| 41  | Not Used                  | 42  | Not Used                  |

| 43  | Not Used                  | 44  | Not Used                  |

| 45  | Not Used                  | 46  | Not Used                  |

| 47  | IO27 / LVDS1-             | 48  | IO28                      |

| 49  | 1029                      | 50  | IO30 / LVDS1+             |

| 51  | Not Used                  | 52  | Not Used                  |

#### **Connector Details**

The PC-104 connector is optional, and its fitment and choice of connector depends on the selections made in the product configuration sheet. The options are:

Samtec SSQ-126-21-G-D Samtec SSQ-126-23-G-D Samtec SSQ-126-04-G-D Samtec ESQ-126-38-G-D Samtec ESQ-126-39-G-D Samtec ESQ-126-49-G-D Samtec TSW-126-07-G-D

Two connectors are used, one each for H1 and H2. Instead of fitting the connectors, wires down to 26 AWG in thickness may be soldered directly into the connector through-hole pads with the adjacent through-hole pads used as strain relief.

# 4.5.1.1.2 High-Speed Interface (P5)

The CE provides a high-speed board-to-board connector supporting very high data rates. The connector pinout is shown in Table 4-3. Do not connect to the pins labelled 'Reserved'. The 'CE\_on' signal can be used to determine the power status of the CE: this signal is pulled up to 3.3 V through a 10 k $\Omega$  resistor on the CE. The LVDS signals can also be configured as 3.3 V LVCMOS compatible single-ended I/O's. The PowerCtrl signal is routed directly to the power switch. See 4.5.1.2 for details. The signals 'I<sup>2</sup>C SDA' and 'I<sup>2</sup>C SCL' are both routed directly to the I<sup>2</sup>C buffer. See 4.5.1.3.1 for details. The high-speed interface provides access to the power, control and data interfaces meaning it can be used as the one and only interface to the CE without requiring the PC104 interface. Default signal assignments are shown in the tables.

Table 4-5: High-Speed Interface Connector (P5) Pinout

| Pin | Signal                | Default IO Assignment | Pin | Signal                | Default IO Assignment |

|-----|-----------------------|-----------------------|-----|-----------------------|-----------------------|

| 1   | Signal GND            |                       | 2   | Signal GND            |                       |

| 3   | Reserved <sup>1</sup> |                       | 4   | Reserved <sup>1</sup> |                       |

| 5   | Reserved <sup>1</sup> |                       | 6   | Reserved <sup>1</sup> |                       |

| 7   | Signal GND            |                       | 8   | Signal GND            |                       |

| 9   | Reserved <sup>1</sup> |                       | 10  | Reserved <sup>1</sup> |                       |

| 11  | Reserved <sup>1</sup> |                       | 12  | Reserved <sup>1</sup> |                       |

| 13  | Signal GND            |                       | 14  | Signal GND            |                       |

| 15  | Reserved <sup>1</sup> |                       | 16  | Reserved <sup>1</sup> |                       |

| 17  | Reserved <sup>1</sup> |                       | 18  | Reserved <sup>1</sup> |                       |

| 19  | Signal GND            |                       | 20  | Signal GND            |                       |

| 21  | Reserved <sup>1</sup> |                       | 22  | Reserved <sup>1</sup> |                       |

| Pin | Signal                | Default IO Assignment   | Pin | Signal                | Default IO Assignment |

|-----|-----------------------|-------------------------|-----|-----------------------|-----------------------|

| 23  | Reserved <sup>1</sup> |                         | 24  | Reserved <sup>1</sup> |                       |

| 25  | Signal GND            |                         | 26  | Signal GND            |                       |

| 27  | Reserved <sup>1</sup> |                         | 28  | Reserved <sup>1</sup> |                       |

| 29  | Reserved <sup>1</sup> |                         | 30  | Reserved <sup>1</sup> |                       |

| 31  | Signal GND            |                         | 32  | Signal GND            |                       |

| 33  | Reserved <sup>1</sup> |                         | 34  | Reserved <sup>1</sup> |                       |

| 35  | Reserved <sup>1</sup> |                         | 36  | Reserved <sup>1</sup> |                       |

| 37  | Signal GND            |                         | 38  | Signal GND            |                       |

| 39  | Reserved <sup>1</sup> |                         | 40  | Reserved <sup>1</sup> |                       |

| 41  | Reserved <sup>1</sup> |                         | 42  | Reserved <sup>1</sup> |                       |

| 43  | Signal GND            |                         | 44  | Signal GND            |                       |

| 45  | Reserved <sup>1</sup> |                         | 46  | Reserved <sup>1</sup> |                       |

| 47  | Reserved <sup>1</sup> |                         | 48  | Reserved <sup>1</sup> |                       |

| 49  | Signal GND            |                         | 50  | Signal GND            |                       |

| 51  | Reserved <sup>1</sup> |                         | 52  | Reserved <sup>1</sup> |                       |

| 53  | Reserved <sup>1</sup> |                         | 54  | Reserved <sup>1</sup> |                       |

| 55  | Signal GND            |                         | 56  | Signal GND            |                       |

| 57  | IO31                  | PPS                     | 58  | IO32 / LVDS8+         | HS_RR+ / US_nCTS+     |

| 59  | CE_on                 |                         | 60  | IO33 / LVDS8-         | HS_RR- / US_nCTS-     |

| 61  | Signal GND            |                         | 62  | Signal GND            |                       |

| 63  | IO34 / LVDS9+         | HS_Ctrl+ / US_EOF+      | 64  | IO36 / LVDS10+        | HS_D1+                |

| 65  | 1035 / LVDS9-         | HS_Ctrl- / US_EOF-      | 66  | IO37 / LVDS10-        | HS_D1-                |

| 67  | Signal GND            |                         | 68  | Signal GND            |                       |

| 69  | IO38 / LVDS11+        | HS_D0+ / US_TxData+     | 70  | IO40 / LVDS12+        | HS_Clk+ / US_Clk+     |

| 71  | IO39 / LVDS11-        | HS_D0- / US_TxData-     | 72  | IO41 / LVDS12-        | HS_Clk- / US_Clk-     |

| 73  | Signal GND            |                         | 74  | Signal GND            |                       |

| 75  | IO42 / LVDS13+        | SPI_SCK                 | 76  | IO44 / LVDS14+        | SPI_nSEL              |

| 77  | IO43 / LVDS13-        | Driven '0' <sup>1</sup> | 78  | IO45 / LVDS14-        | SPI_MOSI              |

| 79  | Signal GND            |                         | 80  | Signal GND            |                       |

| 81  | IO46 / LVDS15+        | SPI_MISO                | 82  | IO48 / LVDS16+        | not used <sup>1</sup> |

| 83  | IO47 / LVDS15-        | Driven '0' <sup>1</sup> | 84  | IO49 / LVDS16-        | not used <sup>1</sup> |

| 85  | Signal GND            |                         | 86  | 5 V RETURN            |                       |

| 87  | PowerCtrl             |                         | 88  | I <sup>2</sup> C SDA  |                       |

| 89  | 5 V RETURN            |                         | 90  | 5V RETURN             |                       |

| 91  | 5 V RETURN            |                         | 92  | I <sup>2</sup> C SCL  |                       |

| 93  | 5 V RETURN            |                         | 94  | 5 V RETURN            |                       |

| 95  | 5 V                   |                         | 96  | 5 V                   |                       |

| 97  | 5 V                   |                         | 98  | 5 V                   |                       |

| 99  | 5 V                   |                         | 100 | 5 V                   |                       |

1. Do not connect

#### **Connector Details**

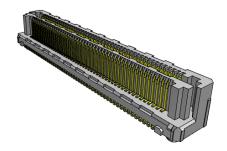

A Samtec LSHM-150-02.5-L-DV-A-N connector is used. A rendering of the connector is shown in Figure 4-8. Note the connector is hermaphroditic: pin 1 mates to pin 2.

Figure 4-8: High-Speed Data Connector (P5)

The CE PCB has mounting holes, fitted with M2 threaded nuts, either side of this connector that can be used to fasten the mating circuit to the CE. Details of the mounting holes are shown in Figure 4-5. Pin 1 is located as per the recommended PCB layout prescribed by Samtec.

# **Bi-Lobe Breakout Adapter**

The Imager can optionally be supplied with a breakout adapter that adapts the LSHM connector (P5) to an Omnetics MNSO-37-AA-N-ETH-M (P9). The preassembled mating connector, MNPO-37-WD/WC, with custom 18 inch long harness is also available. The pinout is provided in Table 4-6, including the default IO assignments. Wire is 30AWG throughout, with shielded twisted pair for the LVDS pairs.

Table 4-6: High-Speed Interface Bi-Lobe Connector (P9) Pinout

| Pin | Signal               | Default IO Assignment             | Pin | Signal         | Default IO Assignment |

|-----|----------------------|-----------------------------------|-----|----------------|-----------------------|

| 1   | 5 V                  |                                   | 20  | 5 V            |                       |

| 2   | I <sup>2</sup> C SCL |                                   | 21  | 5 V            |                       |

| 3   | I <sup>2</sup> C SDA |                                   | 22  | 5 V RETURN     |                       |

| 4   | PowerCtrl            |                                   | 23  | 5 V RETURN     |                       |

| 5   | IO49 / LVDS16-       | SpW_SOUT- / not used <sup>1</sup> | 24  | 5 V RETURN     |                       |

| 6   | IO48 / LVDS16+       | SpW_SOUT+ / not used <sup>1</sup> | 25  | IO45 / LVDS14- | SpW_SIN- / SPI_MOSI   |

| 7   | Signal GND           | LVDS14 Shield                     | 26  | IO44 / LVDS14+ | SpW_SIN+ / SPI_nSEL   |

| 8   | IO47 / LVDS15-       | SpW_DOUT- / SPI_GND <sup>1</sup>  | 27  | Signal GND     | LVDS15 Shield         |

| 9   | IO46 / LVDS15+       | SpW_DOUT+ / SPI_MISO              | 28  | IO41 / LVDS12- | HS_Clk- / US_Clk-     |

| 10  | Signal GND           | LVDS12 Shield                     | 29  | IO40 / LVDS12+ | HS_Clk+ / US_Clk+     |

| 11  | IO43 / LVDS13-       | SpW_DIN- / SPI_GND <sup>1</sup>   | 30  | Signal GND     | LVDS13 Shield         |

| 12  | IO42 / LVDS13+       | SpW_DIN+ / SPI_SCK                | 31  | IO37 / LVDS10- | HS_D1-                |

| 13  | Signal GND           | LVDS10 Shield                     | 32  | IO36 / LVDS10+ | HS_D1+                |

| 14  | IO39 / LVDS11-       | HS_D0- / US_TxData-               | 33  | Signal GND     | LVDS11 Shield         |

| Pin | Signal         | Default IO Assignment | Pin | Signal        | Default IO Assignment |

|-----|----------------|-----------------------|-----|---------------|-----------------------|

| 15  | IO38 / LVDS11+ | HS_D0+ / US_TxData+   | 34  | IO33 / LVDS8- | HS_RR- / US_nCTS-     |

| 16  | Signal GND     | LVDS8 Shield          | 35  | IO32 / LVDS8+ | HS_RR+ / US_nCTS+     |

| 17  | IO35 / LVDS9-  | HS_Ctrl- / US_EOF-    | 36  | Signal GND    | LVDS9 Shield          |

| 18  | IO34 / LVDS9+  | HS_Ctrl+ / US_EOF+    | 37  | IO31          | PPS                   |

| 19  | CE on          |                       |     |               |                       |

<sup>1.</sup> Do not connect

#### **Datamate Breakout Adapter**

The Imager can optionally be supplied with a breakout adapter that adapts the LSHM connector (P5) to a Harwin M80-5424205 (P9). The pinout is provided in Table 4-7, including the default IO assignments.

Table 4-7: High-Speed Interface Datamate Connector (P9) Pinout

| Pin | Signal               | Default IO Assignment             | Pin | Signal         | Default IO Assignment            |

|-----|----------------------|-----------------------------------|-----|----------------|----------------------------------|

| 1   | IO31                 | PPS                               | 22  | CE_on          |                                  |

| 2   | IO32 / LVDS8+        | HS_RR+ / US_nCTS+                 | 23  | Signal GND     | LVDS8 Shield                     |

| 3   | IO33 / LVDS8-        | HS_RR- / US_nCTS-                 | 24  | IO34 / LVDS9+  | HS_Ctrl+ / US_EOF+               |

| 4   | Signal GND           | LVDS9 Shield                      | 25  | IO35 / LVDS9-  | HS_Ctrl- / US_EOF-               |

| 5   | IO36 / LVDS10+       | HS_D1+                            | 26  | Signal GND     | LVDS10 Shield                    |

| 6   | IO37 / LVDS10-       | HS_D1-                            | 27  | IO38 / LVDS11+ | HS_D0+ / US_TxData+              |

| 7   | Signal GND           | LVDS11 Shield                     | 28  | IO39 / LVDS11- | HS_D0- / US_TxData-              |

| 8   | IO40 / LVDS12+       | HS_Clk+ / US_Clk+                 | 29  | Signal GND     | LVDS12 Shield                    |

| 9   | IO41 / LVDS12-       | HS_Clk- / US_Clk-                 | 30  | IO42 / LVDS13+ | SpW_DIN+ / SPI_SCK               |

| 10  | Signal GND           | LVDS13 Shield                     | 31  | IO43 / LVDS13- | SpW_DIN- / SPI_GND <sup>1</sup>  |

| 11  | IO44 / LVDS14+       | SpW_SIN+ / SPI_nSEL               | 32  | Signal GND     | LVDS14 Shield                    |

| 12  | IO45 / LVDS14-       | SpW_SIN- / SPI_MOSI               | 33  | IO46 / LVDS15+ | SpW_DOUT+ / SPI_MISO             |

| 13  | Signal GND           | LVDS15 Shield                     | 34  | IO47 / LVDS15- | SpW_DOUT- / SPI_GND <sup>1</sup> |

| 14  | IO48 / LVDS16+       | SpW_SOUT+ / not used <sup>1</sup> | 35  | Signal GND     | not used                         |

| 15  | IO49 / LVDS16-       | SpW_SOUT- / not used <sup>1</sup> | 36  | Signal GND     | not used                         |

| 16  | PowerCtrl            |                                   | 37  | 5 V RETURN     |                                  |

| 17  | I <sup>2</sup> C SDA |                                   | 38  | 5 V RETURN     |                                  |

| 18  | I <sup>2</sup> C SCL |                                   | 39  | 5 V RETURN     |                                  |

| 19  | 5 V RETURN           |                                   | 40  | 5 V RETURN     |                                  |

| 20  | 5 V                  |                                   | 41  | 5 V            |                                  |

| 21  | 5 V                  |                                   | 42  | 5 V            |                                  |

#### 4.5.1.2 Power Interface

The CE requires a regulated 5 V  $\pm$  10% Direct Current (DC) supply at a current of at least 1.5 A. This DC input power supply is filtered on the CE using a discrete Electro-Magnetic Interference (EMI) filter. The nominal DC current consumption for the different modes in the operational state is given in Table 4-8.

Table 4-8: Nominal Imager Power Consumption Values at Room Temperature

| Operational Mode | Beginning of Life (BOL) | After 25 krad TID |

|------------------|-------------------------|-------------------|

| Idle Mode (1)    | 470 mA                  | 495 mA            |

| Imaging Mode (2) | 1100 mA                 | 1160 mA           |

| Readout Mode (3) | 470 mA                  | 495 mA            |

- (1) CE is powered on, but the FEE is off. Control and High-Speed Data interfaces are static.

- (2) CE and FEE are powered on, and an image is being captured.

- (3) CE is powered on, but the FEE is off. Control and High-Speed Data interfaces are active.

The 5 V supply must be supplied by one, or a combination, of the PC104 connector pins H1.47, H1.49, H1.51, H2.13, H2.15, H2.16, H2.25, and H2.26, or the high-speed interface connector pins P5.95, P5.96, P5.97, P5.98, P5.99 and P5.100. The ground connection is made by one, or a combination, of PC104 connector pins H2.29, H2.30, and H2.32, or the high-speed interface connector pins P5.86, P5.89, P5.90, P5.91, P5.93, P5.94.

The CE has an optional power switch onboard that can be used to switch power to the Imager on. This may be used if the 5 V supplied to the CE is not switched. If this power switch option is selected in the product configuration sheet, its control line 'PowerCtrl' can be routed to one of the PC104 connector pins H1.4, H1.5, H1.6, H1.7, H1.8, H1.9, H1.10, H1.11, H1.13, H1.14, H1.15, H1.16, H2.17, H2.18, H2.19 or H2.20, or the high speed connector pin P5.87. The 'PowerCtrl' control signal is active high. To turn on the CE, the 'PowerCtrl' control signal must be driven high by applying a voltage between 2.5 V and 5.0 V for at least 100 ms.

The 'PowerCtrl' signal may optionally be used to power the CE off (as well as on). If this option is selected the Imager can be turned off by driving 'PowerCtrl' low to between 0 V and 0.5 V for at least 100 ms. This option can be enabled in the product configuration sheet. If this option is selected, the CE will power-cycle itself in the event of a radiation induced overcurrent condition.

The 'PowerCtrl' signal may optionally be latched onboard the CE. If this option is enabled, the 'PowerCtrl' signal may be deasserted after the CE has switched on (after 100 ms) which enables the CE to turn the Imager completely off in the event of a radiation induced overcurrent condition. This option can be enabled in the product configuration sheet. The 'CE\_on' signal, or an unused 'IOn' signal, may be used as feedback and will be driven high when the imager is powered on and pulled to GND when the imager is turned off.

#### 4.5.1.3 Control Interface

This interface is used to command the CE and receive telemetry from the CE. The imager acts as a slave on the control interface. The standard control interface is I<sup>2</sup>C and SPI (both run in parallel), but UART (RS-422/RS-485) and SpaceWire is also supported. The master provides a single ID byte to the imager, which identifies the specific command or request. The master may then continue a command transaction by writing one or more

parameter bytes to the imager. In the case of request transactions, the master will read data bytes from the imager.

The ID byte is partitioned as follows:

| Transaction Type | ID Byte Range |

|------------------|---------------|

| Command          | 0x00 – 0x7F   |

| Request          | 0x80 - 0xFF   |

Since the ID byte is unique for each command or request, it is used to determine the length and the structure of the remaining transaction bytes (payload). Little-endian mode is used for parameters and data that span multiple bytes. The paragraphs that follow provide more information on the physical interface layers.

#### 4.5.1.3.1 I<sup>2</sup>C Interface

The CE implements an I<sup>2</sup>C slave interface compliant to Standard-mode and Fast-mode as defined in [2]. Depending on the selections made in the product configuration sheet, the I<sup>2</sup>C Interface can operate at either 3.3 V or 5 V voltage levels and supports 7-bit slave addressing.

The SCL signal can be routed from either H1.21, H1.43 or P5.92 and the SDA signal from either H1.23, H1.41 or P5.88 depending on the selections made in the product configuration sheet. The I<sup>2</sup>C signals are buffered using an NXP PCA9517ADP and can optionally be pulled up to the bus voltage (3.3 V or 5 V as configured) if enabled in the product configuration sheet. The I<sup>2</sup>C slave address is taken from the product configuration sheet.

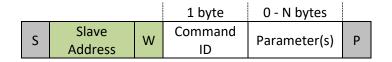

#### **Command Transactions**

Command transactions are in the form of an I<sup>2</sup>C write transfer, with a mandatory Command ID byte, followed by optional parameter bytes.

Figure 4-9: I<sup>2</sup>C Command Transaction

### **Request Transactions**

Request transactions are in the form of a combined write-read transfer. An I<sup>2</sup>C write transfer of the Request ID byte is immediately followed by a I<sup>2</sup>C read transfer of one or more data bytes.

Figure 4-10: I<sup>2</sup>C Request Transaction

#### 4.5.1.3.2 SPI Interface

In addition to the I<sup>2</sup>C interface, the CE also implements a 3.3 V LVCMOS compatible SPI slave interface consisting of four signals. These four signals can be routed to the 'IOn' pins on the physical electrical interfaces as defined in 4.5.1.1. The four SPI signals are:

- nSEL Active low select signal generated by the master to select the slave interface. When not active (high) the SPI interface is not selected and placed in its reset state. All communication is initiated by the master first driving this nSEL signal low. It is kept low for the duration of the communication.

- MOSI Master Out Slave In signal is the data output of the master.

- MISO Master In Slave Out is the data output of the slave.

- SCK The serial clock signal driven by the master. The maximum clock rate is 1 MHz.

The SPI interface conforms to the SPI standard "00" (clock polarity '0', clock phase '0'). As such the values on the MOSI and MISO lines are valid at the rising edge of SCK and remain valid until the next SCK shift edge.

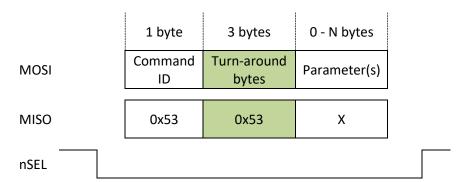

#### **Command Transactions**

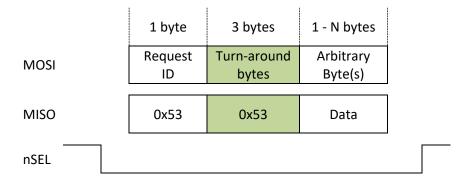

Command transactions require the SPI master to send a sequence of bytes on the MOSI line, as shown in Figure 4-11, consisting of a Command ID byte, followed by three mandatory turn-around bytes, then optional parameter bytes. The turn-around bytes may have an arbitrary value. The bytes received by the master (on the MISO line) are not used.

Figure 4-11: SPI Command Transaction

#### **Request Transactions**

Request transactions require the SPI master to send a sequence of bytes on the MISO line, as shown in Figure 4-12, consisting of a Request ID byte, followed by three mandatory turn-around bytes, then one or more arbitrary bytes (depending on the length of the requested data). The turn-around bytes may have arbitrary value. The bytes received by the master (on the MISO line), after the turn-around bytes have been sent, represent the return data. In other words, the first 4 bytes received on the MISO line should be ignored.

Figure 4-12: SPI Request Transaction

#### 4.5.1.4 Data Interface

The imager provides a high-speed data interface consisting of up to seven LVDS pairs that can be routed to any 'LVDS $n\pm$ ' pin pair on the PC-104 interface (4.5.1.1.1) or the High-Speed Interface (4.5.1.1.2). Two output link protocols are supported: the Simera Sense Standard LVDS link; and the USART link. The Simera Sense Standard High-Speed LVDS, USART, and SpaceWire protocols are supported.

#### 4.5.1.4.1 Standard High-Speed LVDS Link

The standard high-speed link consists of a clock, a synchronisation channel, a receiver ready line, and 1, 2 or 4 data lanes. The clock is free running and activated as soon as the interface is enabled for data read out. The bit rate can be set from 100 to 800 Mbps (per data lane) and the clocking can be configured to be single data rate (SDR) or double data rate (DDR). 800 Mbps is only supported in DDR. Various clock alignment options are also available.

Up to seven LVDS pairs are used:

- HS\_Clk Clock to which HS\_D[n] and HS\_Ctrl is synchronised.

- HS\_D[0-3] The data Lanes. The standard high-speed link can be configured to use 1, 2 or 4 lanes

- HS\_Ctrl Conveys synchronisation and other out-of-band status information for the entire link

- HS RR Optionally returned from the data sink to provide flow control

When using the standard high-speed link, the data interface has three possible states:

- OFF The interface is turned off and all output signals (all except HS\_RR) are driven low.

- INACTIVE HS\_Clk is running. HS\_Ctrl has the "SYNC" bit set ('1') properly, however, the "LA" bit is cleared ('0'), and no data is sent.

- ACTIVE HS\_Clk is running. HS\_Ctrl has both "SYNC" and "LA" bits set ('1'). Valid data may be sent in this state, as indicated by the "DV" bit.

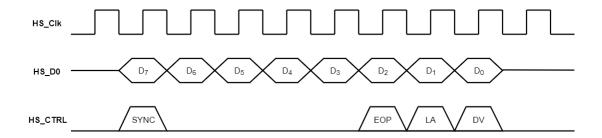

Data is transferred in bytes of 8 bits, most significant bit (MSB) first. The most basic one byte transfer cycle using a single data lane is shown in Figure 4-13.

Figure 4-13: Standard High-Speed Link Byte Transfer Cycle Waveform

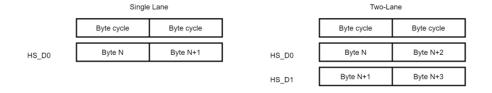

Single vs two data lane byte ordering is shown in Figure 4-14.

Figure 4-14: Single vs Two Data Lane Byte Ordering

The information in the HS\_Ctrl channel is applicable to all data lanes. The bits are defined as follow:

- SYNC This is the byte synchronisation bit which is used to mark the start of a new byte. It is always set ('1') when the link is in any state other than the OFF state.

- EOP The end of packet bit is set during the transfer of the last byte of a data packet. Data is formatted into packets (see Section 4.5.1.4.3) and this bit can be used to indicate the boundary between packets.

The EOP bit will only be set when the link is in ACTIVE state and a valid byte is output (DV bit is set, '1').

- LA This bit indicates the links state. It is set when the link is in ACTIVE state.

- DV The data byte(s) on the data lane(s) are valid only when this bit is set ('1').

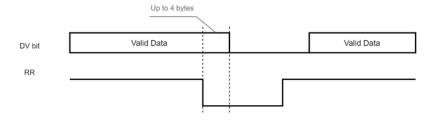

HS\_RR allows the data sink to throttle the flow of data. When HS\_RR is asserted ('1'), the receiver is ready to accept more data. When HS\_RR is deasserted ('0') the interface is requested to stop transmitting and will do so by setting the DV bit low ('0'). The interface will wait in this state indefinitely until HS\_RR is asserted ('1'). The interface may transmit up to 4 bytes once the data sink sets HS\_RR low ('0'). The receiver should therefore be willing to receive up to 4 more valid bytes after setting HS\_RR low ('0'). This is shown in Figure 4-15.

Figure 4-15: High-Speed Link HS\_RR Operation

#### 4.5.1.4.2 USART Link

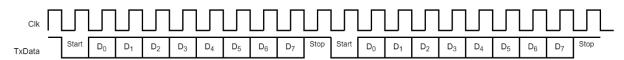

The USART Link consists of a clock, data, clear-to-send, and end-of-frame signals. The clock is free running and activated as soon as the interface is enabled for data read out. Data is transmitted in 10-bit transfers (a start bit, 8 data bits, and a stop bit) similar to a UART, but synchronised to the clock. The basic transfer is shown in Figure 4-16.

Figure 4-16: USART Data Transfer

The USART link does not make provision for multiple data lanes. The bit rate (baud rate) can be set from 400 kbps up to 25 Mbps. Four LVDS pairs are used:

- US Clk Clock to which US TxData and US EOF is synchronised.

- US TxData The data line. When the interface is idle, this line is driven high ('1').

- US\_nCTS Active low "clear to send" signal driven by the data sink (receiver) to perform flow control. The data interface transmits data while US\_nCTS is asserted ('0') and will stop transmitting when deasserted ('1').

- US\_EOF This is an "end of frame" signal pulsed high after the last data byte has been transmitted.

When using the USART link, the data interface has three possible states:

- OFF The interface is turned off. US\_Clk and US\_EOF are driven low ('0'), while US\_TxData is driven high ('1').

- INACTIVE US\_Clk is running. US\_EOF is driven low ('0') and US\_TxData is driven high ('1').

- ACTIVE US\_Clk is running. Valid data may be sent in this state.

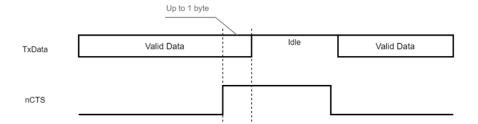

The operation of US\_nCTS is shown in Figure 4-17. Once US\_nCTS is de-asserted ('1'), the interface will finish the current byte before returning the US\_TxData line to the Idle state ('1'). The interface will wait in this state indefinitely until US\_nCTS is asserted ('0').

Figure 4-17: USART US\_nCTS Operation

The US\_EOF line is used to indicate the end of the data frame. It is always exactly 10 US\_Clk cycles long and will never be asserted ('1') less than 40 US\_Clk cycles after the last valid data byte is transmitted. It may however be asserted ('1') more than 40 US\_Clk cycles after the last valid data byte is transmitted. The operation of US\_EOF is shown in Figure 4-18.

Figure 4-18: USART US\_EOF Operation

#### 4.5.1.4.3 Data Format

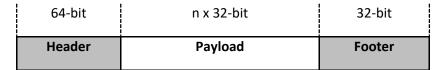

Image data is stored in the Flash memory in a packet-based format which may be read out via the Data Interface as a continuous stream. During an imaging session, the pixel data from each sensor line is formatted into individual packets which are time stamped. Additional packets are injected into the stream in real time, so that relevant ancillary data from the user and imager may be included. User ancillary packets are generated using data received from the satellite bus, which typically includes attitude data, ephemeris data and timing information. Imager ancillary packets allow the exact imager settings applied during the session to be stored. Each packet includes a header, payload and footer. The header is used to identify the packet and extract the variable length payload. The payload content is uniquely defined for each identifier. The footer is in the form of a CRC-32 applied to the full packet. The packet format is shown in Figure 4-19.

Figure 4-19: Imager Data Packet Description

A typical imaging session will generate a stream of packets as shown in Figure 4-20.

| Session Start                            |

|------------------------------------------|

| Imager Ancillary Data                    |

| User Ancillary Data (2)                  |

| Time Sync <sup>(2)</sup>                 |

| Scene Start                              |

| Exposure Start                           |

| Line Data (Band 0, Line 0)               |

| Exposure Start                           |

| Line Data (Band 0, Line 1)               |

|                                          |

| Exposure Start                           |

| Line Data (Band 0, Line 8)               |

| Thumbnail Line Data (Band 0, Line 0) (3) |

| Exposure Start                           |

|                                          |

| Exposure Start                           |

| Line Data (Band 0, Line 288)             |

| Thumbnail Line Data (Band 0, Line 36)    |

| Exposure Start                           |

| Line Data (Band 0, Line 289)             |

| Line Data (Band 1, Line 0)               |

| Exposure Start                           |

| Line Data (Band 0, Line 290)             |

| Line Data (Band 1, Line 1)               |

|                                          |

| Exposure Start                           |

| Line Data (Band 0, Line 578)             |

| Imager Ancillary Data <sup>(1)</sup>     |

| Line Data (Band 1, Line 289)             |

| User Ancillary Data (2)                  |

| Line Data (Band 2, Line 0)               |

|                                          |

| Imager Ancillary Data (1)                |

| User Ancillary Data (2)                  |

| End Session                              |

|                                          |

- (1) Injected by Imager automatically

- (2) Injected as user provides command via Control Interface

- (3) Assumes thumbnail reduction factor of 8

Figure 4-20: Data Output Example for an Imaging Session

# 4.5.1.5 Grounding

All mounting holes on the CE are connected to each other and to GND through a broadband 100 nF ceramic capacitor to facilitate grounding. The FEE is grounded to the OFE through a 470 k $\Omega$  resistor.

#### 4.6 Environmental Interfaces

#### 4.6.1 Thermal Radiation Interface

#### 4.6.1.1 Interface 8: xScape100 VIS OFE to Environment

The front aperture of the OFE exchanges heat through thermal radiation with the space environment at the aperture. The function of this interface is to transmit thermal energy between the OFE and the space environment by means of radiation.

#### 4.6.2 Cosmic Radiation Interfaces

#### 4.6.2.1 Interface 9: Environment to xScape100 VIS OFE

There is an interface between the space environment and the OFE through which cosmic radiation is transmitted to the OFE.

# 4.6.2.2 Interface 10: Environment to TriScape100 Sensor Unit

There is an interface between the space environment and the TriScape100 Sensor Unit through which cosmic radiation is transmitted to the sensor unit.

# 4.6.2.3 Interface 11: Environment to TriScape100 Control Electronics

There is an interface between the space environment and the CE through which cosmic radiation is transmitted to the CE.

# 5. Environmental Requirements

# 5.1 Transportation

#### 5.1.1 Temperature

During transportation and in a non-operating condition the maximum temperature of the Imager assembly shall not exceed 50 °C and the minimum temperature of the Imager assembly shall not be less than -10 °C.

#### 5.1.2 Humidity

The humidity during transportation shall be less than 60%, non-condensing.

#### 5.1.3 Shock/Vibration

All handling operations shall limit the peak acceleration exposure of the Imager to less than 25 g, in any direction.

#### 5.1.4 Cleanliness

During transportation, the Imager shall be kept in an environment with a cleanliness level equal to or better than International Organization for Standardization (ISO) class 8, as per ISO 14644-1:2015 standards.

#### 5.2 Storage

During storage it is assumed that the Imager will not be in motion, therefore vibration and shock loading conditions are not relevant. During storage, the following conditions shall be adhered to:

#### 5.2.1 Temperature

During prolonged storage and in a non-operating condition the maximum temperature of the Imager shall not exceed 30 °C and the minimum temperature of the Imager shall not be less than 10 °C.

# 5.2.2 Humidity

The humidity during prolonged storage shall be between 30% and 60%, non-condensing.

#### 5.2.3 Cleanliness

The Imager shall be stored in an environment with a cleanliness level equal to or better than ISO class 8, as per ISO 14644-1:2015 standards.

#### 5.3 Assembly, Integration and Testing

All Assembly, Integration and Testing (AIT) procedures shall be performed in an ISO class 8 cleanroom, as per ISO 14644-1:2015 standards, or better. In addition, during AIT the following conditions shall always be adhered to:

#### 5.3.1 Shock

All handling operations shall limit shock exposure of the complete OFE assembly to less than 30 g for 10 ms, in any direction.

#### 5.3.2 Mechanical Interface with OFE

During all AIT procedures, all mechanical mating interfaces with the OFE shall cause zero relative displacement (in the x-y plane) between any of the OFE's four mounting points.

#### 5.4 In-Orbit

#### 5.4.1 Survivable Temperature

To ensure survival, the maximum temperature of the Imager shall not exceed 65 °C and the minimum temperature of the Imager shall not be less than -25 °C.

#### 5.4.2 Operating Temperature

During operation, the maximum temperature of the Imager shall not exceed 50 °C and the minimum temperature of the Imager shall not be less than -10 °C.

#### **5.4.3** Operating Temperature Gradients

During operation, the maximum axial temperature gradient over the OFE shall not be greater than 3 °C. During operation, the maximum transverse (radial) temperature gradient over the OFE shall not be greater than 2 °C.

#### 5.4.4 Outgassing of Satellite Components

Material used in satellite components, which are near the Imager, shall have a maximum Total Mass Loss (TML) of less than 1.0% and a maximum Collected Volatile Condensable Material (CVCM) of less than 0.10%. Refer to [1] for a list of material TML and CVCM data.

# **Contact Us**

# Simera Sense (Pty) Ltd

Old Paardevlei Road

Somerset West, 7130

South Africa

info@simera-sense.com

www.simera-sense.com