150-Watt CubeSat Electronic Power System (EPS)

# 150-Watt CubeSat Electrical Power System (EPS)

## **Technical Reference Manual**

## Disclaimer

ALL PRODUCT. PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE. Ibeos, its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "lbeos"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any reference manual or in any other disclosure relating to any product. Ibeos makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Ibeos disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability. Statements regarding the suitability of products for certain types of applications are based on Ibeos's knowledge of typical requirements that are often placed on Ibeos's products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify lbeos's terms and conditions of purchase, including but not limited to the warranty expressed therein. Except as expressly indicated in writing, Ibeos products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Ibeos product could result in personal injury or death. Customers using or selling lbeos products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Ibeos personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Ibeos.

150-Watt CubeSat Electronic Power System (EPS)

## **TABLE OF CONTENTS**

| 1 | App        | rovals and Tracking                     | 5   |

|---|------------|-----------------------------------------|-----|

| • | 1.1        | Signatures                              |     |

|   | 1.2        | Revision History                        |     |

| 2 |            | bnyms                                   |     |

| 3 |            | duction                                 |     |

| J | 3.1        | Document Purpose                        |     |

|   | 3.2        | System Overview                         |     |

|   | 3.2<br>3.3 | •                                       |     |

| 4 |            | Block Diagram                           |     |

| 4 |            | dling and Storage Guidelines            |     |

|   | 4.1        | General Handling.                       |     |

|   | 4.2        | Electro-Static Discharge                |     |

| - | 4.3        | Storage                                 |     |

| 5 |            | em Specifications                       |     |

|   | 5.1        | Absolute Maximum Operating Conditions   |     |

|   | 5.2        | Recommended Operating Conditions        |     |

|   | 5.3        | Specifications                          |     |

|   | 5.4        | General Specifications                  |     |

|   | 5.4.1      |                                         |     |

|   | 5.4.2      | - <b>G</b>                              |     |

|   | 5.4.3      |                                         |     |

|   | 5.4.4      |                                         |     |

|   | 5.4.       | · · · · · · · · · · · · · · · ·         |     |

|   | 5.4.6      | 6 Spacecraft Watchdog Specifications    | .15 |

|   | 5.4.7      | 7 Housekeeping Specifications           | .15 |

|   | 5.4.8      | 3 Internal Watchdog Specifications      | .15 |

| 6 | Syst       | em Initialization                       | .16 |

|   | 6.1        | Spacecraft Inhibits                     | .16 |

|   | 6.2        | Separation Switches                     | .16 |

|   | 6.3        | EPS Start-Up                            | .17 |

|   | 6.3.1      | Normal Start-up                         | .17 |

|   | 6.3.2      | 2 Start-up During Battery Undervoltage  | .18 |

| 7 | Batt       | ery Charge Regulator                    | .20 |

|   |            |                                         | .20 |

|   | 7.2        | Solar Array Voltage Control             | .20 |

|   | 7.2.1      |                                         |     |

|   | 7.2.2      | 5 5                                     |     |

|   | 7.3        | Power Supply Interface Power Transients |     |

|   | 7.3.       |                                         |     |

| 8 | -          | ched Outputs                            |     |

| 5 | 8.1        | Overview and Configurability            |     |

|   | 8.2        | Switched Output Operation               |     |

|   | 8.3        | Switched Output Rise/Fall Time          |     |

|   | 8.4        | Switched Output Insertion Loss          |     |

|   | J.T        | omitoriou output indonitori E000        |     |

150-Watt CubeSat Electronic Power System (EPS)

|    | 8.5     | Switched Output Inrush Transients                       | .24 |

|----|---------|---------------------------------------------------------|-----|

|    |         | Latching Over-Current Protection                        |     |

|    |         | Parallel Connection of Switched Outputs                 |     |

| 9  |         | netry                                                   |     |

|    |         | Overview                                                |     |

|    | 9.2     | System Telemetry Transfer Functions                     | .26 |

|    | 9.2.1   |                                                         |     |

|    | 9.2.2   | Linear Transfer Functions                               | .26 |

|    | 9.3     | Telemetry Error                                         | .28 |

|    | 9.3.1   | Analog Circuit Error                                    | .28 |

|    | 9.3.2   | Single Event Effects                                    | .28 |

| 1( | ) Fault | Protection                                              | .29 |

|    | 10.1    | Power Converter Overcurrent Protection                  | .29 |

|    | 10.2    | Battery Overvoltage / Overcharge Current Protection     | .29 |

|    | 10.2.   | 1 Battery Bus Abnormal Transient Voltage Protection     | .29 |

|    | 10.3    | Battery Undervoltage / Overdischarge Current Protection |     |

|    | 10.4    | Internal Watchdog Timer                                 |     |

|    | 10.5    | Switch 1-4 Overcurrent Protection                       | .31 |

|    | 10.6    | Battery Over-Temperature Protection                     | .31 |

|    | 10.7    | External Watchdog Timer                                 | .31 |

|    | 10.7.   | •                                                       |     |

|    | 10.7.   |                                                         |     |

|    | 10.8    | Fault Reporting                                         |     |

|    | 10.9    | Event Counters                                          | .34 |

| 11 | Elect   | rical Interfaces                                        | .35 |

|    | 11.1    | J3 – Battery/Solar Array Connector                      | .35 |

|    | 11.2    | J2 – Switched Output and Serial I/F Connector           |     |

|    | 11.3    | J1 - Ground Support Equipment (GSE) Connector           |     |

| 12 | 2 Com   | mand, Control, and Data Handling Interface              |     |

|    | 12.1    | Overview                                                |     |

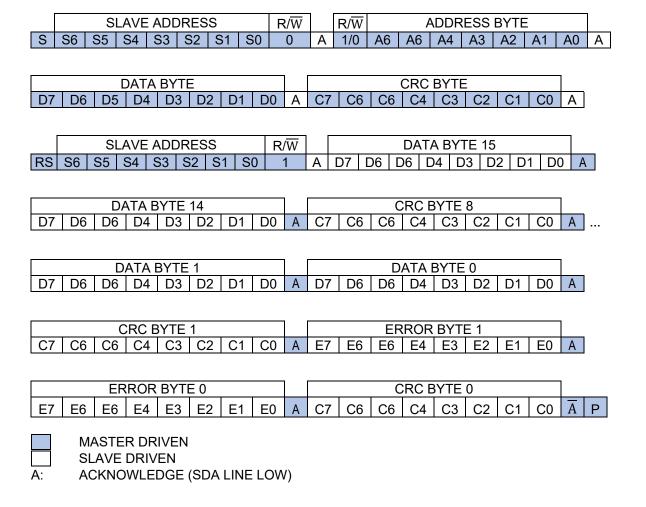

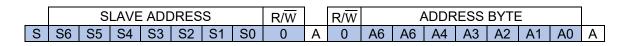

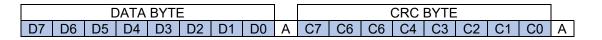

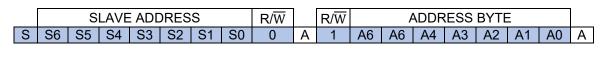

|    | 12.2    | Inter-Integrated Circuit (I2C) Interface                | .38 |

|    | 12.2.   | •                                                       |     |

|    | 12.2.   | 2 Additional Bus Pull-Ups                               | .38 |

|    | 12.2.   | 3 Timing Diagram                                        | .39 |

|    | 12.2.   |                                                         |     |

|    | 12.2.   | 5 General Call Address                                  | .39 |

|    | 12.2.   |                                                         |     |

|    | 12.2.   | 7 Transaction Timeout                                   | .43 |

|    | 12.3    | Serial Peripheral Interface (SPI)                       |     |

|    | 12.3.   |                                                         |     |

|    | 12.3.   |                                                         |     |

|    | 12.3.   | •                                                       |     |

|    | 12.3.   | ,                                                       |     |

|    | 12.3.   | 5 5                                                     |     |

150-Watt CubeSat Electronic Power System (EPS)

|    | 12.3.6 | Transaction Structure                   | 48 |

|----|--------|-----------------------------------------|----|

| 12 | 2.4    | Cyclic Redundancy Check (CRC)           | 52 |

| 12 | 2.5    | Error Flags                             | 53 |

|    | 12.5.1 | Battery Protection Fault                | 54 |

|    | 12.5.2 | Battery Undervoltage Fault              | 54 |

|    | 12.5.3 | Switched Output n Over-Current          | 55 |

|    | 12.5.4 | CC&DH WDT Timeout                       | 55 |

| 12 | 2.6    | Register Details                        | 55 |

|    | 12.6.1 | Register Summary                        | 55 |

|    | 12.6.2 | System Configuration Registers          | 56 |

|    | 12.6.3 | System Control Registers                | 57 |

|    | 12.6.4 | System Telemetry Banks                  | 58 |

|    | 12.6.5 | System Status Registers                 | 60 |

|    | 12.6.6 | Error Registers                         | 61 |

|    | 12.6.7 | System Identification Registers         | 62 |

| 13 | Mechai | nical/Thermal Interface                 | 63 |

| 13 | 3.1    | Thermal Considerations                  | 63 |

| 14 | System | 1 Testing                               | 64 |

| 15 | Append | dix A: Hardware Configurable Parameters | 66 |

| 16 | Append | dix B: Software Configurable Parameters | 67 |

| 17 | Append | dix C: Reference Test Data              | 67 |

150-Watt CubeSat Electronic Power System (EPS)

#### **1 APPROVALS AND TRACKING**

#### 1.1 Signatures

Prepared by: John Bevilacqua, Ibeos

Director of Engineering

Signature

Date

*Approved by:* Abigail Davidson, Ibeos Director of Programs

Signature

Date

## 1.2 Revision History

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date       | Approval |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| -        | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4/1/2019   | RVR      |

| A        | Updated 5V bus converter short circuit current; Updated power converter specifications<br>to reflect further testing. Updated Switch 1 output current transfer function. Added detail<br>to the BCR current control section. Added CRC generation code example. Reduced<br>default maximum battery charge current. Updated solar array voltage range. Updated<br>switch, power converters, BCR specifications based on final test results. Added timing<br>specifications for SPI polling scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4/11/2019  | SHW      |

| В        | Added current limits and rise times for unswitched bus interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4/23/2019  | JJB      |

| С        | Corrected a sign error in the transfer function for the solar array voltage configuration register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8/15/2019  | JJB      |

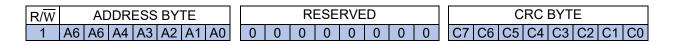

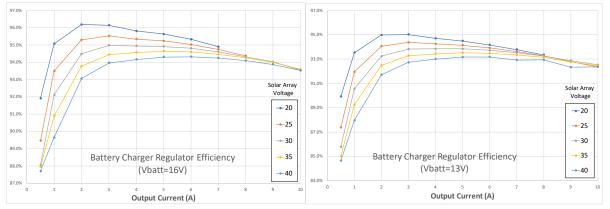

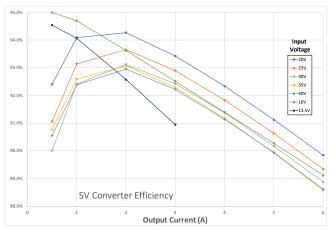

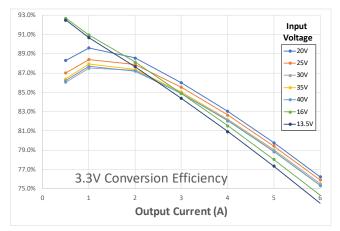

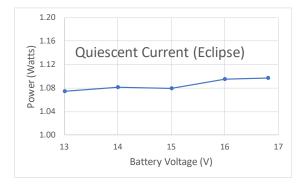

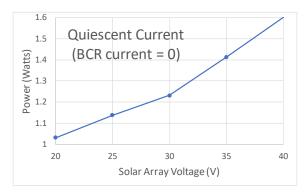

| D        | Added reference efficiency plots in appendix C, added max converter capacitance limits (was TBD), adjusted limit for 12V step load voltage transient, updated SW1-5 fall time from 1 ms to 0.25ms. Added switched output parallel connection section. Updated switch 6-10 rise/fall times. Split battery bus max capacitance into unswitched bus and combined (switched plus unswitched bus).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10/24/2019 | JJB      |

| E        | Updated BCR and 5V foldback current limits to 7.5A nominal; Updated BCR maximum current from 10A to 7A. Adjusted PPT voltage step size from 75 to 150 mV and slew rate from 2.25 to 4.5V/sec. Removed TBC from max BCR output capacitance. Reduced maximum 12V short circuit current from 11A to 9A. Adjusted 12V efficiency to 93.6% and 94.2% nominal. Updated Battery overcurrent Charge threshold from 16A to 14A nominal. Added recommendations for unswitched battery bus loads to ensure robust undervoltage recovery. Added BCR foldback operation details to Section 7. 30V housekeeping supply fault protection removed due to design eliminating drop-out sources that could be caused by 12V overcurrent. This removed Section 10.6, 12.6.5.3, 12.5.5, the relevant error bits in 12.5 and 12.6.6.1, and register description in 12.6.1. Added section 13.1, Thermal Considerations. Updated start-up specifications and descriptions in Section 6.3. Updated figures and tables regarding WDT resets in Section 10.7. Updated transfer function and default and max values for MBCCCR register (Section 12.6.2.2). Updated battery undervoltage fault to include 3.3-Volt converter disable (Section 12.5.2). Updated latching over-current protection time to trip (Section 8.6). Moved SPI transaction timeout section beneath Timing Specification (Section 12.3.5.5). | 12/5/2019  | JJB      |

| F        | Added Section 15 and captured errata related to the Battery Protection Fault Counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/2/2020   | JJB      |

150-Watt CubeSat Electronic Power System (EPS)

|   | Updated BCR Turn-on Delay in Table 5.<br>Updated Turn-On Time in Table 4.                                                            |     |

|---|--------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Updated SPI timing parameters (Min and Nominal) in Table 28.<br>Added drop-out time for switch 1-5 SEE event in sections 3.2 and 8.2 |     |

|   | Updated Table 6, Regulated Bus Power Converter Specs, 3.3V parameter values.                                                         |     |

| G | Updated switch turn-on delay time in 8.2 from ~5 ms to ~2 ms                                                                         | JJB |

150-Watt CubeSat Electronic Power System (EPS)

## 2 ACRONYMS

## 3 INTRODUCTION

#### 3.1 Document Purpose

This document intends to provide all information necessary to implement this system in a spacecraft-level assembly. It describes the specifications of the system, system handling and storage guidelines, the electrical power interfaces, the CC&DH interfaces, and system testing guidelines. Note that the EPS ICD is the sole reference for specifications and recommendations regarding connector locations, mass, and mechanical and thermal interface considerations.

#### 3.2 System Overview

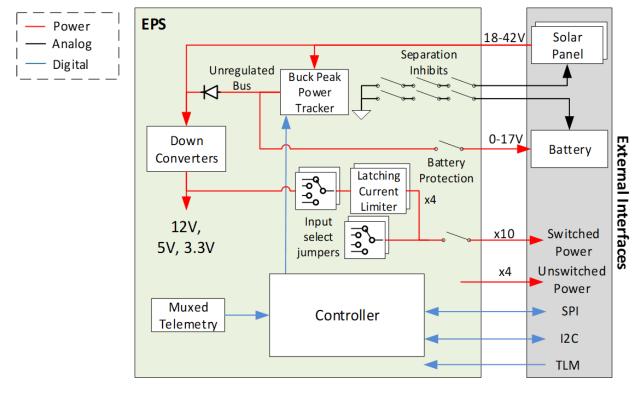

The Ibeos 150-Watt CubeSat Electrical Power System is a radiation-tolerant and reliable power conditioning and distribution system with comprehensive system-wide fault tolerance. The high-level features of the EPS include:

- Full system radiation tolerance up to 30 kRad(Si) TID, operating through SEEs with an LET of up to 37 MeV-cm<sup>2</sup>/mg and surviving SEEs with an LET of up to 55 MeV-cm<sup>2</sup>/mg.

- Switched outputs 1-5 can have short interruptions due to SEE events, but will not turn-on due to an SEE

- Efficient solar array power conversion and battery charging via single-input maximum power point tracker with a 7A rated output current

- Overall power handling capability of up to 150W

- Regulated 12-Volt, 5-Volt, and 3.3-Volt outputs

- Unregulated battery bus outputs

- 10 switched power outputs

- 8x solder-jumper-configurable to 3.3-Volt, 5-Volt, 12-Volt or unregulated battery busses

- 4 with slow rise time, current telemetry, and latching over-current protection

- 4 with fast rise time

- 2x unregulated battery power for battery heaters

- Unswitched power outputs

- SPI and I2C CC&DH interface for system commanding, control, and telemetry acquisition

- Spacecraft-level configurable watchdog timer via CC&DH interface

150-Watt CubeSat Electronic Power System (EPS)

### 3.3 Block Diagram

Figure 1. EPS Functional Block Diagram

## 4 HANDLING AND STORAGE GUIDELINES

The specific handling and storage guidelines for the EPS are included below. Failure to follow these guidelines may result in damage to the EPS hardware or degradation in system performance.

#### 4.1 General Handling

During all handling of the EPS system, care must be taken to keep the system clear of any contaminants, both conductive and non-conductive. Foreign object debris can create circuit shorts which can permanently alter system performance even after the FOD is removed.

<u>Caution</u>: When integrated with a battery, extra caution must be taken to not short terminations that have un-fused battery power on them. Failing to do so may result in hazards.

It is recommended that gloves we worn when handling EPS flight units to minimize the transfer of oils and outgassing materials.

It is recommended that flight units be removed from the delivery packaging and handled only in a cleanliness-controlled environment.

#### 4.2 Electro-Static Discharge

The EPS implements several electronic devices that are sensitive to ESD and therefore the circuit card must only be handled in a static-dissipative environment with proper ESD protective equipment.

#### 4.3 Storage

The EPS is delivered in anti-static packaging with a hygroscopic drying agent to keep the relative humidity of the packaged system very low. Upon receipt of EPS units, it is recommended that they be stored in an anti-static, humidity-controlled environment with a temperature between 20°C and 40°C. In this environment, the EPS can be stored for up to 3 years.

#### 5 SYSTEM SPECIFICATIONS

#### 5.1 Absolute Maximum Operating Conditions

Table 1. Absolute Maximum Operating Conditions

| Parameter                  | Min | Max | Units |

|----------------------------|-----|-----|-------|

| Solar Array Voltage        | 0   | 42  | V     |

| Battery Voltage            | 0   | 19  | V     |

| Card Interface Temperature | -35 | 70  | °C    |

#### 5.2 Recommended Operating Conditions

Table 2. Recommended Operating Conditions

| Parameter                  | Min  | Max  | Units |

|----------------------------|------|------|-------|

| Solar Array Voltage        | 19   | 40   | V     |

| Battery Voltage            | 13.2 | 16.8 | V     |

| Card Interface Temperature | -25  | 60   | °C    |

#### 5.3 Specifications

Unless otherwise noted, the conditions in the table below apply to the specification in this section.

Table 3. Default Conditions for EPS Specifications

| Parameter                           | Value | Units |

|-------------------------------------|-------|-------|

| Card Interface Temperature          | 25    | С°    |

| SA MPP Voltage, V <sub>SA,MPP</sub> | 24    | V     |

| Battery Voltage, V <sub>Batt</sub>  | 16    | V     |

#### 5.4 General Specifications

### Table 4. General Specifications

| Parameter                   | Conditions                                                              | Min | Nom | Max | Units |

|-----------------------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

| Quiescent Power Consumption | Switched outputs off,<br>V <sub>Batt</sub> =16 V, V <sub>SA</sub> =40 V | -   | 1.4 | -   | W     |

| Quiescent Power Consumption | Switched outputs off,<br>V <sub>Batt</sub> =16 V, V <sub>SA</sub> =0 V  | -   | 1.1 | -   | W     |

| Quiescent Power Consumption | Undervoltage,<br>V <sub>Batt</sub> =16 V, V <sub>SA</sub> =40 V         | -   | 0.9 | -   | W     |

| Quiescent Current           | Any inhibit closed,<br>V <sub>Batt</sub> =16 V                          | -   | 0.2 | 0.3 | mA    |

| Quiescent Current           | Undervoltage active<br>V <sub>Batt</sub> =10 V, V <sub>SA</sub> =0 V    | -   | 6   | 8   | mA    |

| Solar Array Current per Pin | -                                                                       | 0   | 1   | 2   | Α     |

150-Watt CubeSat Electronic Power System (EPS)

| Parameter    | Conditions                                       | Min | Nom | Max | Units |

|--------------|--------------------------------------------------|-----|-----|-----|-------|

| Turn-On Time | Time from inhibit released to accepting commands | -   | 400 | -   | msec  |

| Mass         | CCA only; not including<br>Wedge-Loks, etc.      | -   | 140 | -   | g     |

## 5.4.1 Battery Charge Regulator (BCR) Specifications

#### Table 5. BCR Specifications

| Parameter                                             | Conditions                                                            | Min  | Nom      | Max     | Units |

|-------------------------------------------------------|-----------------------------------------------------------------------|------|----------|---------|-------|

| Battery Voltage                                       | Operating                                                             | 13.2 | -        | 16.8    | V     |

| Charge Current Ripple                                 | Charging                                                              | -    | 45       | -       | mA    |

| Battery Charge Current                                |                                                                       | See  | e Sectio | n 12.6. | 2.2   |

| Efficiency                                            | Excludes EPS quiescent<br>current, 5 A out                            | 93   | 95       | 96.5    | %     |

| Output Current Limit                                  | Charge current plus<br>battery bus loading                            | -    | -        | 7       | А     |

| Overcurrent Limit                                     | Foldback                                                              | -    | 7.5      | -       | Α     |

| MPPT Slew rate                                        | -                                                                     | -    | 4.5      | -       | V/sec |

| MPPT Step Size                                        | -                                                                     | -    | 150      | -       | mV    |

| Battery Bus Voltage, Protection<br>Mode               | No battery connected or<br>during overvoltage<br>protection           | -    | 21       | -       | V     |

| Default V <sub>SA</sub>                               | Peak power tracking<br>disabled                                       | -    | 19       | -       | V     |

| Turn-on Delay                                         | Time from power applied to BCR providing current                      | -    | 990      | -       | msec  |

| Charge Current Refresh Rate                           | -                                                                     | -    | 30       | -       | Hz    |

| V <sub>SA</sub> Refresh Rate (peak power<br>tracking) | -                                                                     | -    | 30       | -       | Hz    |

| Charge Current Step Size                              |                                                                       | -    | 45       | -       | mA    |

| Maximum output capacitance                            | Battery bus unswitched<br>outputs (external)                          | -    | 100      | -       | uF    |

| Maximum output capacitance                            | Combined battery bus<br>switched and unswitched<br>outputs (external) | -    | 500      | -       | uF    |

## 5.4.2 Regulated Bus Power Converter Specifications

| <b>T</b> / / 0 |           | -   | -     | <b>^</b> ( | 0 10 11        |

|----------------|-----------|-----|-------|------------|----------------|

| Table 6.       | Regulated | Bus | Power | Converter  | Specifications |

| Parameter      | Conditions | Min  | Nom  | Max  | Units |

|----------------|------------|------|------|------|-------|

| 12V Converter  |            |      |      |      |       |

| Output Voltage | DC         | 11.6 | 12.1 | 12.4 | V     |

| Output Voltage | DC + AC    | 10.8 | -    | 13.2 | V     |

150-Watt CubeSat Electronic Power System (EPS)

| Parameter                     | Conditions                                                               | Min  | Nom  | Max           | Units |

|-------------------------------|--------------------------------------------------------------------------|------|------|---------------|-------|

| Efficiency, Battery Input     | Excludes EPS quiescent current, 3 A out, V <sub>SA</sub> =0 V            | 91   | 93.6 | 95.5          | %     |

| Efficiency, Solar Array Input | Excludes EPS quiescent<br>current, 3 A out, V <sub>SA</sub> =30<br>V     | 93   | 94.2 | 95.5          | %     |

| Output Ripple Voltage (ac)    | -                                                                        | -    | 10   | 50            | mV    |

| Transient Response            | 0 A to 1.5 A                                                             | -300 | 150  | -             | mV    |

| Transient Response            | 1.5 A to 0 A                                                             | -    | 150  | -300          | mV    |

| Rise Time                     | -                                                                        | 1    | 4    | 10            | msec  |

| Output Current                | -                                                                        | 0    | -    | 4             | Α     |

| Short Circuit Current         | -                                                                        | 5    | 7    | 9             | Α     |

| Load Capacitance              | External to unit, all<br>switched and unswitched<br>12V outputs combined | 0    | -    | 500           | uF    |

| 5V Converter                  |                                                                          |      |      |               |       |

| Output Voltage                | DC                                                                       | 4.75 | 5.0  | 5.25          | V     |

| Output Voltage                | DC + AC                                                                  | 4.5  | 5.0  | 5.5           | V     |

| Efficiency, Battery Input     | Excludes EPS quiescent current, 5 A out, V <sub>SA</sub> =0 V            | 88   | 91   | 92            | %     |

| Efficiency, Solar Array Input | Excludes EPS quiescent<br>current, 5 A out, V <sub>SA</sub> =30<br>V     | 90   | 92   | 94            | %     |

| Output Ripple Voltage (AC)    | -                                                                        | -    | 10   | 50            | mV    |

| Transient Response            | 0 A to 3 A                                                               | -150 | -75  | -             | mV    |

| Transient Response            | 3 A to 0 A                                                               | -    | 75   | 150           | mV    |

| Rise Time                     | -                                                                        | 1    | 10   | 30            | msec  |

| Output Current                | -                                                                        | 0    | -    | 6             | Α     |

| Short Circuit Current         | -                                                                        | 6.5  | 7.5  | 9             | Α     |

| Load Capacitance              | External to unit                                                         | 0    | -    | 1000          | uF    |

| 3.3V Converter                |                                                                          |      |      |               |       |

| Output Voltage                | DC                                                                       | 3.15 | 3.3  | 3.45          | V     |

| Output Voltage                | DC + AC                                                                  | 3    | 3.3  | 3.6           | V     |

| Efficiency                    | Excludes EPS quiescent current, 3 A out, V <sub>SA</sub> =0 V            | 88   | 91   | 94            | %     |

| Output Ripple Voltage (ac)    | -                                                                        | -    | 10   | 50            | mV    |

| Transient Response            | 0 A to 1.5 A                                                             | -200 | -50  | -             | mV    |

| Transient Response            | 1.5 A to 0 A                                                             | -    | 50   | 150           | mV    |

| Rise Time                     | -                                                                        | 1    | 10   | 30            | msec  |

| Output Current                | -                                                                        | 0    | -    | 3             | Α     |

| Short Circuit Current         | -                                                                        | 6    | 7    | 9.5           | A     |

| Load Capacitance              | External to unit                                                         | 0    | -    | 1000<br>[TBC] | uF    |

150-Watt CubeSat Electronic Power System (EPS)

## 5.4.3 Switched Output Specifications

Table 7. Switched Output Specifications

| Parameter             | Conditions | Min  | Nom  | Max | Units |

|-----------------------|------------|------|------|-----|-------|

| Switched Outputs 1-5  |            |      |      |     |       |

| Rise Time             | -          | 0.5  | 1    | 2   | msec  |

| Fall Time             | -          | -    | 0.25 | -   | msec  |

| SW 1 Current (Note 1) | -          | -    | -    | 6   | Α     |

| SW 2 Current (Note 1) | -          | -    | -    | 4.5 | Α     |

| SW 3 Current (Note 1) | -          | -    | -    | 3   | Α     |

| SW 4 Current (Note 1) | -          | -    | -    | 3   | Α     |

| SW 5 Current          | -          | -    | -    | 2   | Α     |

| Switched Outputs 6-10 |            |      |      |     |       |

| Rise Time             | -          | 0.03 | -    | 0.3 | msec  |

| Fall Time             | -          | -    | 5    | -   | msec  |

| SW 6-10 Current       | -          | -    | -    | 2   | Α     |

1. If output is configured to provide 3.3-Volt or 12-Volt power, the maximum output current is limited by the converter current limit (listed above). These limits may be further bounded by latching current limits.

#### 5.4.4 Unswitched Output Specifications

#### Table 8. Switched Output Specifications

| Parameter                  | Conditions                    | Min | Nom | Max | Units |

|----------------------------|-------------------------------|-----|-----|-----|-------|

| Unregulated Bus            |                               |     |     |     | •     |

| Rise Time                  | Exiting undervoltage          | -   | TBD | -   | msec  |

| Rise Time                  | Separation Inhibit<br>Release | -   | TBD | -   | msec  |

| Maximum Current, DC        | I/O limited                   | -   | -   | 12  | Α     |

| Maximum Current, transient | <1 ms duration                | -   | -   | 24  | Α     |

| 12V Bus                    |                               |     |     |     |       |

| Rise Time                  |                               | -   | 5   | I   | msec  |

| Maximum Current, DC        | I/O limited                   | -   | -   | 2   | A     |

| Maximum Current, transient | <1 ms duration                | -   | -   | 4   | Α     |

| 5V Bus                     |                               |     |     |     |       |

| Rise Time                  |                               | -   | 16  | -   | msec  |

| Maximum Current, DC        | I/O limited                   | -   | -   | 2   | Α     |

| Maximum Current, transient | <1 ms duration                | -   | -   | 4   | Α     |

| 3.3V Bus                   |                               |     |     |     |       |

| Rise Time                  |                               | -   | 1   | -   | msec  |

| Maximum Current, DC        | I/O limited                   | -   | -   | 2   | Α     |

| Maximum Current, transient | <1 ms duration                | -   | -   | 4   | А     |

150-Watt CubeSat Electronic Power System (EPS)

## 5.4.5 Fault Protection Specifications

#### Table 9. Fault Protection Specifications

| Parameter                                   | Conditions | Min  | Nom   | Max   | Units |

|---------------------------------------------|------------|------|-------|-------|-------|

| Battery Under-Voltage Threshold             | Falling    | 12.4 | 12.7  | 12.9  | V     |

| Battery Under-Voltage Threshold             | Rising     | 13.7 | 14.25 | 14.7  | V     |

| Battery Over-Voltage Threshold              | Rising     | 16.9 | 17.3  | 17.55 | V     |

| Battery Over-Voltage Threshold              | Falling    | 16.7 | 17.1  | 17.4  | V     |

| Battery Over-Current Charge Threshold       | -          | 12   | 14    | 16    | А     |

| Battery Over-Current Discharge<br>Threshold | -          | 25   | 33    | 37    | А     |

| Sw. 1 Over-Current Threshold (Note 1)       | -          | 2.5  | 3     | 3.5   | А     |

| Sw. 2 Over-Current Threshold (Note 1)       | -          | 4.05 | 4.5   | 4.95  | Α     |

| Sw. 3 Over-Current Threshold (Note 1)       | -          | 2.7  | 3     | 3.3   | Α     |

| Sw. 4 Over-Current Threshold (Note 1)       | -          | 2.7  | 3     | 3.3   | Α     |

1. Latching current limits are configurable at time of order. See Appendix B: Software Configurable Parameters.

#### 5.4.6 Spacecraft Watchdog Specifications

#### Table 10. Spacecraft Watchdog Specifications

| Parameter                           | Conditions         | Min | Nom | Max | Units |

|-------------------------------------|--------------------|-----|-----|-----|-------|

| No Pet Trip Duration (System Safed) | Default is 128 sec | 1   | 128 | 130 | sec   |

| Post-Trip System Reset Duration     | Non-Global         | 0.5 | 1.2 | 1.5 | sec   |

| Post-Trip System Reset Duration     | Global             | 6   | -   | 11  | sec   |

#### 5.4.7 Housekeeping Specifications

Specifications in this section are for reference only. These pertain solely to internal card functionality.

#### Table 11. Housekeeping Specifications

| Parameter                            | Conditions | Min | Nom  | Max | Units |

|--------------------------------------|------------|-----|------|-----|-------|

| 3.3-Volt Housekeeping Supply Voltage | -          | 3.0 | 3.3  | 3.6 | V     |

| 12-Volt Housekeeping Supply Voltage  | -          | 9   | 11.3 | 12  | V     |

| 30-Volt Housekeeping Supply Voltage  | -          | 24  | 28.5 | 33  | V     |

### 5.4.8 Internal Watchdog Specifications

#### Table 12. Internal Watchdog Specifications

| Parameter                        | Conditions | Min | Nom | Max | Units |

|----------------------------------|------------|-----|-----|-----|-------|

| Internal Watchdog Trip Time      | -          | -   | 3   | -   | sec   |

| Internal Watchdog Reset Duration | -          | -   | 6   | -   | sec   |

## 6 SYSTEM INITIALIZATION

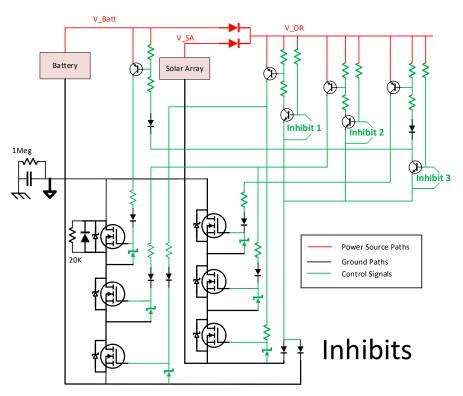

#### 6.1 Spacecraft Inhibits

The spacecraft inhibits are low side series switches that open the connection between both the battery and system ground as well as the solar array and system ground. The only ground path for the battery is through the inhibit switches. The inhibit circuits are single-fault tolerant. The battery and solar array low side inhibits are separate switches in order to ensure that the inhibited EPS provides two-fault tolerance with respect to either powering the spacecraft or charging the battery.

The simplified block diagram below shows the inhibit configuration. The following circuit elements shown are simplified for readability:

- Current sense circuits are not shown

- Gate bias resistor is a simplification of the bias circuit

- The gate-source bleed resistors and timing capacitors are not shown

Figure 2. Simplified Spacecraft Inhibits Schematic

## 6.2 Separation Switches

The spacecraft inhibits, as described in Section 6.1, are to be driven by separation switches. The separation switches are not a part of the EPS CCA. A single separation switch is to be connected across a given  $INHIBIT_n_P1/INHIBIT_n_P2$  pair on the J3 connector. See Section 11.2 for connector pin assignments for the 3 pairs of signals. If fewer than 3 separation inhibits are

150-Watt CubeSat Electronic Power System (EPS)

needed, the unused separation inhibit pins should be left unconnected (open). Separation inhibits should never be connected in parallel with each other or any other connection.

The separation switches behave per Table 13 below.

| Inhibit | Signal Names               | Sep. Switch<br>State | Inhibit State |

|---------|----------------------------|----------------------|---------------|

| 1       | INHIBIT 1 P1, INHIBIT 1 P2 | Closed               | Asserted      |

| ļ       |                            | Open                 | Released      |

| 2       | INHIBIT_2_P1, INHIBIT_2_P2 | Closed               | Asserted      |

| 2       |                            | Open                 | Released      |

| 3       | INHIBIT 3 P1, INHIBIT 3 P2 | Closed               | Asserted      |

| 3       |                            | Open                 | Released      |

#### Table 13. Separation Switch Logic

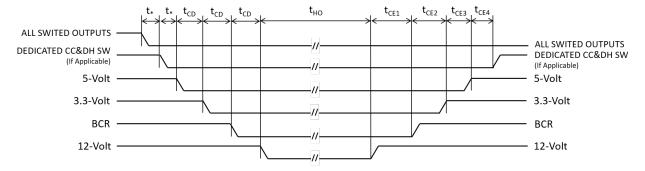

#### 6.3 EPS Start-Up

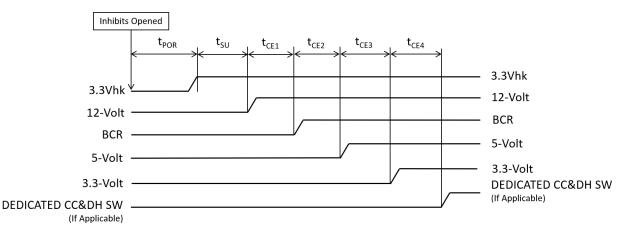

#### 6.3.1 Normal Start-up

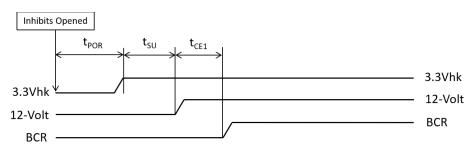

The normal EPS start-up is a sequenced event. First the 3.3-Volt and 12-Volt housekeeping supplies become valid. At this point, all switching power converters are disabled. The microcontroller then goes through the following start-up sequence:

| Table 14. N | <i>lormal</i> EPS | Start-Up | Sequence | Timing Parameters |

|-------------|-------------------|----------|----------|-------------------|

|-------------|-------------------|----------|----------|-------------------|

| Symbol           | Parameter                                              | Condition | Min | Nom | Max | Units |

|------------------|--------------------------------------------------------|-----------|-----|-----|-----|-------|

| <b>t</b> POR     | MCU Power-on-Reset Duration                            | —         | I   | 5   | -   | ms    |

| ts∪              | MCU Initialization Duration                            | —         | I   | 20  | -   | ms    |

| t <sub>CE1</sub> | Converter Enable Command Sequence<br>Interval, 12-Volt | -         | -   | 25  | -   | ms    |

| t <sub>CE2</sub> | Converter Enable Command Sequence<br>Interval, BCR     | -         | -   | 185 | -   | ms    |

| t <sub>CE3</sub> | Converter Enable Command Sequence<br>Interval, 5-Volt  | -         | -   | 90  | -   | ms    |

150-Watt CubeSat Electronic Power System (EPS)

| Symbol                                                                   | Parameter                                            | Condition | Min | Nom | Max | Units |

|--------------------------------------------------------------------------|------------------------------------------------------|-----------|-----|-----|-----|-------|

| t <sub>CE4</sub>                                                         | Converter Enable Command Sequence Interval, 3.3-Volt | _         | Ι   | 20  | Ι   | ms    |

| 1. Timing values are taken at ambient temperature with ne external leads |                                                      |           |     |     |     |       |

1. Timing values are taken at ambient temperature with no external loads.

**Note:** The unregulated battery bus might come up prior to the 12-Volt output if insufficient solar array power is available when the inhibits open.

Following the start-up sequence, the EPS will enter its normal routine which consists of executing several periodic functions including:

- Battery charge regulation

- Solar array power regulation

- Fault detection and recovery

- Telemetry acquisition and serialization

- Flight computer communication

### 6.3.2 Start-up During Battery Undervoltage

The EPS will attempt to start-up whenever the inhibits are released and the battery is above the rising UVP limit. If the battery is below the UVP limit, the EPS will enter a low current state until either the voltage at the battery interface rises or power is available from the solar array interface. Once solar array power is available, the EPS will go through the following start-up sequence:

After enabling the BCR, the EPS will enter its normal routine, as described above, with the following variance(s):

1. Charge the battery at the default charge current, fixed solar array voltage, and EoC battery voltage.

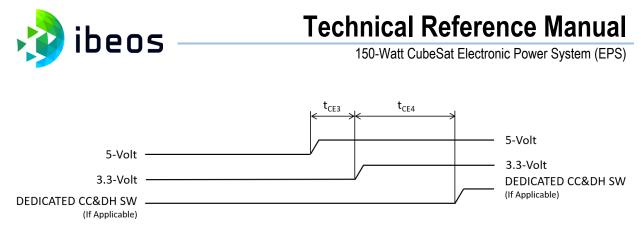

When the battery voltage reaches the rising undervoltage threshold, the EPS will go through the remainder of the start-up sequence as depicted below:

Figure 5. EPS Undervoltage Start-Up Sequence Phase 2

| Table 15. | EPS Underv | oltage Start-Up | Sequence | Timing Parameters |

|-----------|------------|-----------------|----------|-------------------|

|-----------|------------|-----------------|----------|-------------------|

| Symbol           | Parameter                                              | Condition | Min | Nom | Max | Units |

|------------------|--------------------------------------------------------|-----------|-----|-----|-----|-------|

| t <sub>POR</sub> | MCU Power-on-Reset Duration                            |           | I   | 5   |     | ms    |

| ts∪              | MCU Initialization Duration                            | —         | _   | 20  | -   | ms    |

| t <sub>CE1</sub> | Converter Enable Command Sequence<br>Interval, 12-Volt | _         | -   | 25  | -   | ms    |

| t <sub>CE3</sub> | Converter Enable Command Sequence<br>Interval, 5-Volt  | _         | _   | 90  | -   | ms    |

| t <sub>CE4</sub> | Converter Enable Command Sequence Interval, 3.3-Volt   | _         | _   | 20  | -   | ms    |

1. Timing values are taken at ambient temperature with no external loads.

**Note:** The unregulated battery bus might come up prior to the 12-Volt output if insufficient solar array power is available when the inhibits open.

If the available solar array power is low, it may take significant time until the 5-Volt, 3.3-Volt, and dedicated CC&DH switched output (if applicable) are enabled/closed. If the spacecraft is tumbling, it will repeat the sequence in Figure 4 until the battery undervoltage circuit releases.

If the battery is in undervoltage and solar array power is insufficient to supply the quiescent power of the EPS card, it will exhibit a cyclic behavior in which its housekeeping circuits turn on and it begins to sequence up the power converters. The inrush current of the power converters will then cause the solar array voltage to sag. This sag will cause the power converters to turn off due to the housekeeping voltages falling out of regulation. This cycle will repeat until either the available solar array power increases (or the solar array power falls further).

Any loads on the unswitched battery bus should be selected such that they do not cause lock-up during an undervoltage recovery by putting the Battery Charge Regulator into foldback at low voltage. An example of a load that could do this is a constant power converter that operates down to very low voltage. If the converter consumed 40W of power when the BCR output voltage is at 5V, the BCR would be in foldback and unable to provide current to the battery. Undervoltage limits on any constant power unswitched battery bus loads are highly recommended. Unswitched load should be selected that can start up with a constant current source.

## 7 BATTERY CHARGE REGULATOR

The battery charge regulator (BCR) provides power to the battery bus from the solar array. It operates as a downconverter. The input voltage must be at least 10% (approximately) above the battery voltage for it to provide current.

The battery charge regulator operates in two normal modes: battery current control and solar array voltage control as well as an abnormal current foldback mode.

### 7.1 Battery Current Control

The BCR net battery current is commanded by the EPS microcontroller. The commanded current is based on the EoC voltage, battery voltage, and the maximum allowable charge current. The end of charge voltage and maximum allowable charge current are software-controlled parameters that may be adjusted via writes to the following registers.

### 0x10 - Battery End of Charge Voltage (EOCV) Configuration Register

#### 0x11 - Maximum Battery Charge Current Configuration Register

The microcontroller will reduce the commanded current when the measured voltage on the EPS card reaches the EoC voltage to perform a taper charge. Battery voltage is measured locally and will include drops due to the series resistance between the EPS card and the battery along with the internal ESR of the battery.

The commanded battery current can be set to negative values down to approximately -2 A (2-Amp discharge) in order to ensure that the battery can be float charged even if there is an offset error in the telemetry.

The microcontroller updates the commanded battery charge current at 30 Hz. Each update can increase or decrease the commanded current by a single 45 mA step. When the maximum commanded current is increased and sufficient power is available, the battery current will increase in 45 mA steps at 30 Hz up to the new maximum. When the maximum commanded current is decreased and the BCR current loop is in control, the battery current will quickly fall (in less than 200 ms) to the new maximum. The rate of this decrease in current is driven by the BCR hardware control loop.

#### 7.2 Solar Array Voltage Control

### 7.2.1 Constant Voltage Regulation Mode

At start-up, SA voltage control is in a constant voltage regulation mode at a solar array voltage of 19 V. While in this mode, the MCU will command the SA voltage to the value specified by the following configuration register:

#### 0x12 – Solar Array Voltage Configuration Register

The SA voltage control mode is changed between available modes by writing to the following register:

### 0x35 – Peak Power Tracker Control Register

## 7.2.2 Maximum Peak Power Tracking Mode

When MPPT mode is enabled and the measured battery charge current is below the commanded battery charge current (i.e. the solar array is not providing the desired amount of power), the MPPT algorithm takes control and drives the BCR set point. The BCR is put into MPPT mode via the following register:

## 0x35 – Peak Power Tracker Control Register

In MPPT mode, the microcontroller uses a hill-climbing algorithm to find the maximum operating power point of the solar array. The microcontroller calculates solar array power then commands the solar array voltage up or down by one 75 mV step. After taking the step, the new solar array power is calculated and compared to the previous calculation. If the new power is higher, the microcontroller will take another step in the same direction. If the new power is lower, the microcontroller will take a step in the opposite direction. This results in a steady-state behavior in which the solar array walks around the maximum power point with the operating voltage ranging between one step above and one step below the maximum power point (i.e. there will be three observed operating points). If there is significant noise in the system or the change in current is less than one LSB, the peak power tracker may take somewhat longer to adjust to the peak power point.

If the measured solar array current gets below 100 mA, the microcontroller will command the solar array to the default solar array voltage. From there the peak power tracking algorithm will again climb the power slope of the solar array until it reaches a global or local maximum.

It is not recommended to use solar array strings with different numbers of cells as that can create local maxima. If the solar array has more than one maxima, the setpoint can be commanded above them by:

- 1. Entering constant voltage regulation mode

- 2. Setting the minimum solar array voltage to a level above the local maxima

- 3. Enabling MPPT mode

<u>Note:</u> When there is no solar array power, the BCR will operate at zero duty cycle due to the solar array voltage being below the minimum commanded voltage.

### 7.3 **Power Supply Interface Power Transients**

The BCR power converter operates with a voltage mode controller inner loop. As a result, significant changes in the input power supply can generate transient currents and voltages on the output while the feedback amplifiers adjust to the new operating conditions.

If the EPS is connected to a high ESR load on the battery interface such as an electronic load operating in constant voltage mode, this may cause nuisance trips on the battery fault protection circuits. It is recommended that a large capacitance be added in parallel with an electronic load if the EPS is being operated without an actual battery.

## 7.3.1 BCR Foldback

When the BCR output current is commanded to be above 7.5A (nominal value) with a solar array capable of supplying that power into the BCR via a combination of charge current and battery bus loads, the converter will enter a current limit mode in order to provide thermal protection of the main switching devices. This limit was selected based on thermal testing that showed operation within de-rated limits with the board thermal interface temperature near the 70 degree C qualification level and a high overall board power dissipation configuration. The limit varies somewhat with solar array voltage with a typical limit of 7.5A at 19V and 8.1A at 40V.

In some instances, operating with the BCR in foldback current limit while the solar array is operating near or at the peak power point can cause the BCR to transition between the foldback limit and voltage mode regulation. This is not stressful to the BCR, but can cause higher ripple currents and voltages on the solar array and battery, as well as reduce the efficiency of the solar array due to the variation of the operating voltage. If this is observed, it can be avoided by reducing the commanded battery charge current such that the BCR is not operating in foldback or other configuration adjustments that either increase the solar array power to above the BCR foldback limit or reduce the BCR current to below the foldback limit.

## 8 SWITCHED OUTPUTS

#### 8.1 Overview and Configurability

The EPS has 10 switched outputs. At time of manufacture, switched outputs 1-8 can each be configured to switch either 3.3V power, 5V power, 12V power, or unregulated battery power. Switched outputs 9 and 10 switch unregulated battery power and are dedicated to outputs for battery heaters 1 and 2, respectively.

#### 8.2 Switched Output Operation

The EPS's switched outputs are commandable via register writes over the CC&DH interface. The following registers are relevant to switched output commanding:

- 0x31 Latching Current Limited (LCL) Switched Outputs Control Register

- This register contains the switch state bits for switched outputs 1-4 as well as the respective over-current trip indicator bit for each switch.

- See Section 12.6.3.2 for details on register utilization.

- 0x32 Non-Latching Current Limited Switched Outputs Control Register

- This register contains the switch state bits for switched outputs 5-10.

- See Section 12.6.3.3 for details on register utilization.

By default, switched outputs 1-10 are all open. If a designated CC&DH switched output is configured, the default output is Switch 5 (SW5). If configured, this switch is powered on as part of the system start-up sequence. See Section 6 for details regarding the start-up sequence.

A given switch is closed by writing the relevant switch state bit in the LSOCR or the NLSOCR as a 1. Conversely, a given switch is opened by writing the relevant switch state bit in the LSOCR or the NLSOCR as a 0. When writing to a given switch control register, the changes take effect immediately after reception of a valid write command.

Switches that are closed must have their state bit written as a 1 during future writes if the switch is to stay closed. Switches that are open must have their state bit written as a 0 during future writes if the switch is to stay open.

Writing SW5 open, when configured as the dedicated CC&DH output, is an illegal command that will be ignored. If commanding other switches in the same control register as SW5, write the relevant SW5 bit as a 1. Failing to do this will result in the command being ignored and an "Illegal Command" response being returned.

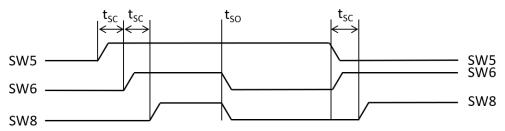

If state changes for multiple switches are commanded via the same register write command, the following sequence is followed:

- 1. Switches to be opened are all simultaneously opened

- 2. Switches to be closed are sequenced on by state bit order (lowest-order bit to highestorder bit)

Figure 6 below depicts this sequencing. The scenario depicted is an NLSOCR value of 0x00 that is rewritten as 0x0B followed by 0x01 and then by 0x0A.

150-Watt CubeSat Electronic Power System (EPS)

#### Table 16. LSOCR Switched Output Command Timing Parameters

| Symbol          | Parameter                                         | Condition | Min | Max | Units |

|-----------------|---------------------------------------------------|-----------|-----|-----|-------|

| t <sub>sc</sub> | Switch Close Command Sequence<br>Interval         | -         | 1   | -   | ms    |

| t <sub>so</sub> | Switch Open Command Sequence<br>Interval (Note 1) | -         | _   | 0   | ms    |

1. All switches written open via the same register write command will be opened at the same time.

Each switch has a SEE filter that prevents an upset on the microcontroller from causing an inadvertent turn-on. This filter also results in there being an  $\sim$ 2 ms second delay between the time when the turn-on/off command is sent from the microcontroller to the start of the switch rise time. This delay can vary by several milliseconds and is in addition to the delay that the microcontroller uses to stagger switch inrush currents.

Switches 6-10 are immune to SEE induced turn-off for SEE levels below 37 MeV-cm<sup>2</sup>/mg. Switches 1-5 can have a drop-out of up to 2 ms due to an SEE event.

### 8.3 Switched Output Rise/Fall Time

Switched outputs 1-5 have enhanced rise time control in order to reduce the inrush current for capacitive loads. These switches have a slow rise time and a fast fall time, relatively. Switched outputs 6-10 have a fast rise time and a slow fall time, relatively.

See Section 5.4.3 for relevant switched output specifications.

### 8.4 Switched Output Insertion Loss

Switched outputs typically have approximately 20-40 m $\Omega$  of series resistance depending on the temperature of the EPS card. It is not recommended to have more than 8 A DC current on any switched output.

### 8.5 Switched Output Inrush Transients

The regulated voltages are current limited by the pulse-by-pulse limit of the 3.3-V, 5-Volt, and 12-Volt power converters. Very high load capacitances may cause there to be sag on the switched output if there is not inrush current limiting on the load. This is a result of the power converters peak current limiting circuits. If there is especially high capacitance on an output, turning that

150-Watt CubeSat Electronic Power System (EPS)

output on while the power converter is operating at lower current will help minimize voltage sag. If the total current on an power converter output is below 50% of the rated maximum when an output is turned on, the maximum recommended switched output capacitance can be increased. The recommended maximum output capacitance for each switch type is listed in Table 17.

| Output<br>Voltage | Max.<br>Capacitance<br>(SW1-5) | Max.<br>Capacitance<br>(SW6-10) | Max.<br>Capacitance<br>(SW1-5) | Max.<br>Capacitance<br>(SW6-10) |

|-------------------|--------------------------------|---------------------------------|--------------------------------|---------------------------------|

|                   | <50% rated o                   | utput current                   | <100% rated                    | output current                  |

| 3.3 V             | 400 uF                         | 120 uF                          | 200 uF                         | 100 uF                          |

| 5.0 V             | 400 uF                         | 120 uF                          | 200 uF                         | 100 uF                          |

| 12.0 V            | 200 uF                         | 47 uF                           | 100 uF                         | 39 uF                           |

| Battery           | 400 uF                         | 47 uF                           | 200 uF                         | 39 uF                           |

| Heater            | N/A                            | 1 uF                            | N/A                            | 1 uF                            |

#### Table 17. Recommended Maximum Switched Output Capacitance

### 8.6 Latching Over-Current Protection

The microcontroller monitors current telemetry for switches 1-4 at a rate of 500 Hz to determine whether any switch is carrying more than its limit. If the measured current exceeds the limit for two or more consecutive samples, the microcontroller sets an overcurrent error status bit for the switch in question and commands the switch open. It takes 7 +/-4 milliseconds from the start of an overcurrent event until the switch opens. The delay is due to the sample rate, consecutive samples, SEE filter delay, and the switch's fall time.

In order to turn on a switch that has experienced an overcurrent event, a command must be sent to clear the overcurrent error prior to or simultaneous with the switch turn-on command.

See Section 12.6.3.2 for more information regarding the over-current flags and control of the latching current limited outputs.

#### 8.7 Parallel Connection of Switched Outputs

Switched outputs should not be connected in parallel without consulting lbeos. The circuit used to enhance turn-off time can have higher than normal dissipation if a DC voltage is applied to it and may result in overstress to the components.

### 9 TELEMETRY

#### 9.1 Overview

The EPS provides 10-bit telemetry for all the key analog voltages, currents, and temperatures on the card. All telemetry measurements are accessible over the CC&DH interface via a master telemetry read command and are organized across the following telemetry banks:

- 0x50 System Voltage Telemetry Bank A

- This telemetry bank contains all available voltage telemetry points.

- See Section 12.6.4.1 for details on this bank.

- 0x52 System Current Telemetry Bank A

- This telemetry bank contains a sub-set of all available current telemetry points.

- See Section 12.6.4.3 for details on this bank.

- 0x53 System Current Telemetry Bank B

- This telemetry bank contains the balance of all available current telemetry points that are not included in SCTBA.

- See Section 12.6.4.4 for details on this bank.

- 0x54 Temperature Telemetry Bank A

- This telemetry bank contains all available temperature telemetry points.

- See Section 12.6.4.6 for details on this bank.

All 10-bit telemetry points are represented and transmitted over the CC&DH interface as digitized voltages. The following section details how to translate such digital values into the analog measurements that they represent.

### 9.2 System Telemetry Transfer Functions

## 9.2.1 Analog Voltage Conversion

A 10-bit digital telemetry point shall be converted to its equivalent analog voltage using the following equation:

where:

V is the equivalent analog voltage X is the 10-bit digital telemetry value

Given this analog voltage between 0V and 2.50V, the linear transfer functions in Section 9.2.2 shall be used to convert this value to the real measurement it represents.

### 9.2.2 Linear Transfer Functions

The following equation shall be used to convert the analog voltage ('V' from Section 9.2.1) to its equivalent real measurement:

$$T = M \times V + B$$

where:

*T* is the real measurement*V* is the analog voltage from Eq. 1*M* is the slope (per following tables)*B* is the Y-intercept (per following tables)

The tables below provide an M and B value for each telemetry point.

### 9.2.2.1 SVTBA Transfer Function Inputs

Eq. 1

Eq. 2

150-Watt CubeSat Electronic Power System (EPS)

#### Table 18. SVTBA Transfer Function Inputs

| TLM<br>POINT | LABEL                         | SLOPE  | Y-INTERCEPT |

|--------------|-------------------------------|--------|-------------|

| 7            | Solar Array Voltage           | 21.000 | 0.000       |

| 6            | Battery Bus Voltage           | 11.000 | 0.000       |

| 5            | 5V Converter Output Voltage   | 3.004  | 0.000       |

| 4            | 12V Converter Output Voltage  | 6.100  | 0.000       |

| 3            | 3.3V Housekeeping Voltage     | 2.000  | 0.000       |

| 2            | 12V Housekeeping Voltage      | 6.100  | 0.000       |

| 1            | 30V Housekeeping Voltage      | 21.000 | 0.000       |

| 0            | 3.3V Converter Output Voltage | 2.000  | 0.000       |

## 9.2.2.2 SCTBA Transfer Function Inputs

#### Table 19. SCTBA Transfer Function Inputs

| TLM<br>POINT | LABEL                        | SLOPE | Y-INTERCEPT |

|--------------|------------------------------|-------|-------------|

| 7            | Solar Array Current          | 4.902 | 0.000       |

| 6            | Battery Charge Current       | 3.887 | -1.961      |

| 5            | 5V Converter Output Current  | 4.902 | 0.000       |

| 4            | 12V Converter Output Current | 2.128 | 0.000       |

| 3            | Switched Output 1 Current    | 5.319 | 0.000       |

| 2            | Switched Output 2 Current    | 2.128 | 0.000       |

| 1            | Switched Output 3 Current    | 2.128 | 0.000       |

| 0            | Switched Output 4 Current    | 2.128 | 0.000       |

## 9.2.2.3 SCTBB Transfer Function Inputs

#### Table 20. SCTBB Transfer Function Inputs

| TLM<br>POINT | LABEL                         | SLOPE  | Y-INTERCEPT |

|--------------|-------------------------------|--------|-------------|

| 7            | Battery Discharge Current     | 20.120 | -10.040     |

| 6            | 3.3V Converter Output Current | 2.128  | 0.000       |

| 5            | N/A                           | N/A    | N/A         |

| 4            | N/A                           | N/A    | N/A         |

| 3            | N/A                           | N/A    | N/A         |

| 2            | N/A                           | N/A    | N/A         |

| 1            | N/A                           | N/A    | N/A         |

| 0            | N/A                           | N/A    | N/A         |

## 9.2.2.4 TTBA Transfer Function Inputs

| TLM<br>POINT | LABEL                     | Thermistor Part Number                                                |

|--------------|---------------------------|-----------------------------------------------------------------------|

| 7            | System Temperature        | B57621C5103J062<br>4.99 kΩ 0.01% pull up to 2.50 V                    |

| 6            | Solar Array Temperature B | Customer Furnished Thermistor 4.99 k $\Omega$ 0.01% pull up to 2.50 V |

| 5            | Solar Array Temperature A | Customer Furnished Thermistor 4.99 k $\Omega$ 0.01% pull up to 2.50 V |

| 4            | Battery Temperature B     | Customer Furnished Thermistor 4.99 k $\Omega$ 0.01% pull up to 2.50 V |

| 3            | Battery Temperature A     | Customer Furnished Thermistor 4.99 k $\Omega$ 0.01% pull up to 2.50 V |

| 2            | N/A                       | N/A                                                                   |

| 1            | N/A                       | N/A                                                                   |

| 0            | N/A                       | N/A                                                                   |

### 9.3 Telemetry Error

### 9.3.1 Analog Circuit Error

Due to component tolerances, leakage currents, and input offsets, each telemetry point will have a slight error factor. If tighter telemetry measurements are required, the delivered test data for a given flight unit may be used to tune out measurement offsets.

Typical full-scale telemetry accuracy over temperature and mission life is within +/-1% for voltage telemetry and +/-3% for current telemetry.

Telemetry values are gathered automatically by the EPS card at a rate of 30 Hz. The telemetry points in a given sample may be gathered up to 33 ms before a telemetry packet is sent. The telemetry points within a packet may also have been gathered up to 33 ms apart.

#### 9.3.2 Single Event Effects

There is the potential for the analog-to-digital converter implemented within the system to upset due to single event effects. Such an upset has the potential to cause an erroneous telemetry value.

**Recommendation:** Due to the SEE susceptibility of the EPS ADC, it is recommended that action never be taken on a single telemetry measurement. Instead, it is recommended that a given telemetry point be requested at least twice (with at least 150 ms of time between requests) to rule out an erroneous ADC reading.

150-Watt CubeSat Electronic Power System (EPS)

## **10 FAULT PROTECTION**

The EPS card has a number of internal hardware and software-based fault protection features designed to minimize the potential of damage to the EPS card as well as the rest of the spacecraft due to anomalous events. These protections include:

- Power converter overcurrent protection

- Switch 1-4 overcurrent protection

- Switched output protection from battery bus abnormal voltage transient events

- EPS internal watchdog timer

- Battery overcurrent, undercurrent, and overvoltage protection

#### **10.1 Power Converter Overcurrent Protection**

The BCR, 3.3-Volt, 5-Volt, and 12-Volt power converters have pulse-by-pulse current limits that cause the converters to fold-back if the maximum output current is exceeded. These limits are detailed in Section 5.4.2. In this mode, the output voltage will sag until the load current decreases to the current limit.

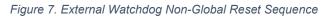

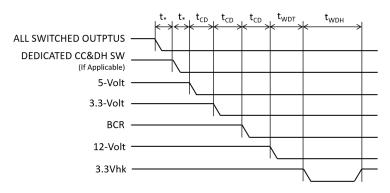

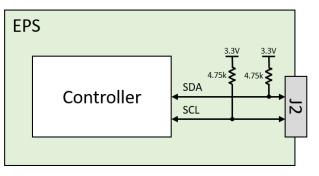

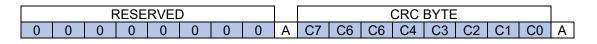

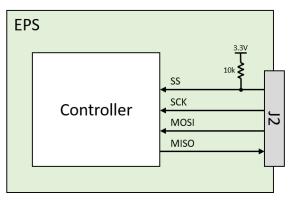

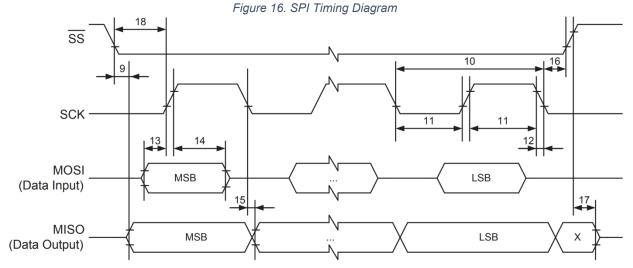

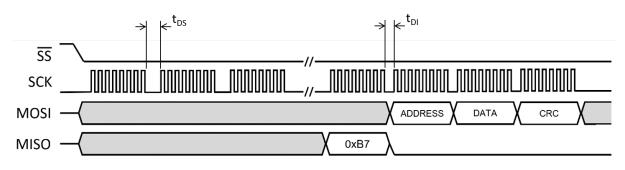

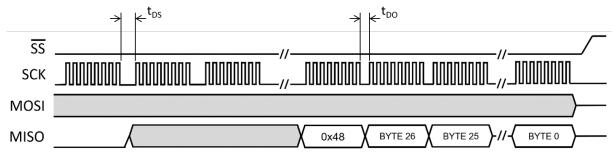

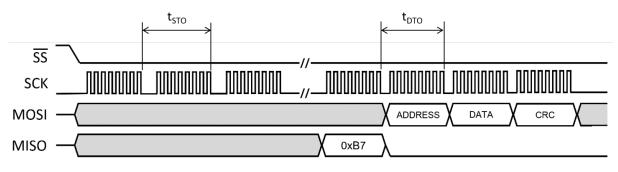

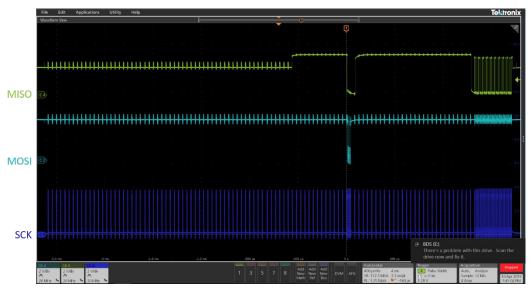

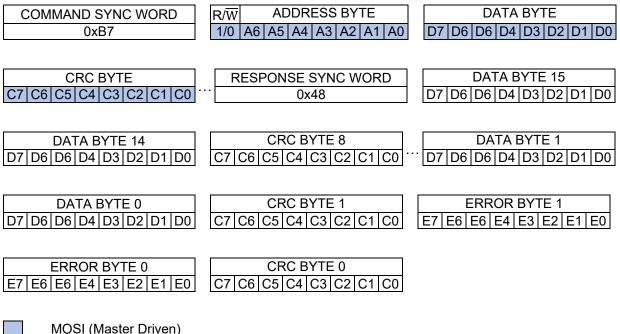

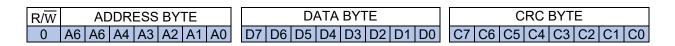

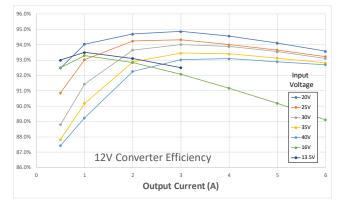

#### 10.2 Battery Overvoltage / Overcharge Current Protection